NAND Flash Memory MT29F4G08AAAWP ... - Micron

NAND Flash Memory MT29F4G08AAAWP ... - Micron

NAND Flash Memory MT29F4G08AAAWP ... - Micron

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

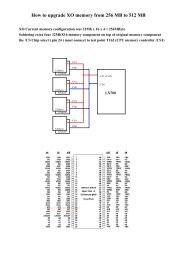

4Gb, 8Gb, and 16Gb x8 <strong>NAND</strong> <strong>Flash</strong> <strong>Memory</strong>Command DefinitionsFigure 29:TWO-PLANE PROGRAM PAGE Operation with RANDOM DATA INPUTtDBSYR/B#I/Ox80h Address (5 cycles)1st plane addressData input 85h Address (2 cycles)Different columnData input 11h 80h(or 81h)Address (5 cycles)2nd plane addressaddress than previous5 address cycles, for1st plane onlyDatainput1Repeat as many times as necessarytPROGR/B#I/Ox85hAddress (2 cycles)Datainput10h1Different columnaddress than previous5 address cycles, for2nd plane onlyRepeat as many times as necessaryTWO-PLANE PROGRAM PAGE CACHE MODE 80h-11h-80h-15hThe TWO-PLANE PROGRAM PAGE CACHE MODE (80h-11h-80h-15h) operation issimilar to the PROGRAM PAGE CACHE MODE (80h-15h) operation. It programs twopages of data from the data registers to the <strong>NAND</strong> <strong>Flash</strong> arrays. The pages must beprogrammed to different planes on the same die. Within a block, the pages must beprogrammed consecutively from the least significant to the most significant pageaddress. Random page programming within a block is prohibited. The first-plane andsecond-plane addresses must meet the two-plane addressing requirements (see “Two-Plane Addressing” on page 35).To enter the two-plane program page cache mode, write the 80h command to thecommand register, write 5 ADDRESS cycles for the first plane, then write the data. Serialdata is loaded on consecutive WE# cycles starting at the given address. Next, write the11h command. The 11h command is a “dummy” command that informs the controllogic that the first set of data for the first plane is complete. No programming of the<strong>NAND</strong> <strong>Flash</strong> array occurs. R/B# goes LOW for t DBSY, then returns HIGH. The READSTATUS (70h) command also indicates that the device is ready when status register bit 6is set to “1.” The only valid commands during t DBSY are READ STATUS (70h) and RESET(FFh).After t DBSY, write the 80h (or 81h) command to the command register, write 5ADDRESS cycles for the second plane, then write the data. The CACHE WRITE (15h)command is written after the second-plane data input is complete. Data is transferredfrom the cache registers to the data registers on the rising edge of WE#. R/B# goes LOWduring this transfer time. After the data has been copied into the data registers and R/B#returns HIGH, memory array programming to both planes begins.PDF: 09005aef81b80e13/Source: 09005aef81b80eac<strong>Micron</strong> Technology, Inc., reserves the right to change products or specifications without notice.4gb_nand_m40a__2.fm - Rev. B 2/07 EN 40 ©2006 <strong>Micron</strong> Technology, Inc. All rights reserved.