AD7008 CMOS DDS Modulator

AD7008 CMOS DDS Modulator

AD7008 CMOS DDS Modulator

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

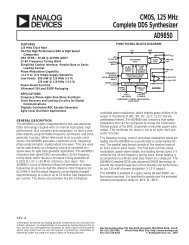

<strong>AD7008</strong>TIMING CHARACTERISTICS (V AA = V DD +5 V ± 5%; T A = T MIN to T MAX , unless otherwise noted)<strong>AD7008</strong>AP20<strong>AD7008</strong>JP50Parameter Min Typ Max Min Typ Max Units Test Conditions/Commentst 1 50 20 ns CLOCK Periodt 2 20 8 ns CLOCK High Durationt 3 20 8 ns CLOCK Low Durationt 4 5 5 ns CLOCK to Control Setup Timet 5 3 3 ns CLOCK to Control Hold Timet 6 4t 1 4t 1 ns LOAD Periodt 7 2t 1 2t 1 ns LOAD High Duration 1t 8 5 5 ns LOAD High to TC0–TC3 Setup Timet 9 5 5 ns LOAD High to TC0–TC3 Hold Timet 10 10 10 ns WR Falling to CS Low Setup Timet 11 10 10 ns WR Falling to CS Low Hold Timet 12 20 20 ns Minimum WR Low Durationt 13 10 10 ns Minimum WR High Durationt 14 3 3 ns WR to D0–D15 Setup Timet 15 3 3 ns WR to D0–D15 Hold Timet 16 20 20 ns SCLK Periodt 17 8 8 ns SCLK High Durationt 18 8 8 ns SCLK Low Durationt 19 10 10 ns SCLK Rising to SDATA Setup Timet 20 10 10 ns SCLK Rising to SDATA Hold TimeNOTE1 May be reduced to 1t 1 if LOAD is synchronized to CLOCK and Setup (t 4 ) and Hold (t 5 ) Times for LOAD to CLOCK are observed.t 1t 3CSCLOCKt 4t 5t 2WRt 10 t 11t 12 t 13FSEL, LOAD,TC3–TC0VALIDVALIDD0–D15t 14 t 15VALID DATAFigure 1. Clock Synchronization TimingFigure 3. Parallel Port TimingLOADt 6t 7t 8t 9SCLKt 20t 16t 17t 19t 18TC0–TC3VALIDSDATADB31DB0Figure 2. Register Transfer TimingFigure 4. Serial Port TimingREV. B –3–