Design Checklist for PowerQUICC II Pro MPC8309 Processor

Design Checklist for PowerQUICC II Pro MPC8309 Processor

Design Checklist for PowerQUICC II Pro MPC8309 Processor

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

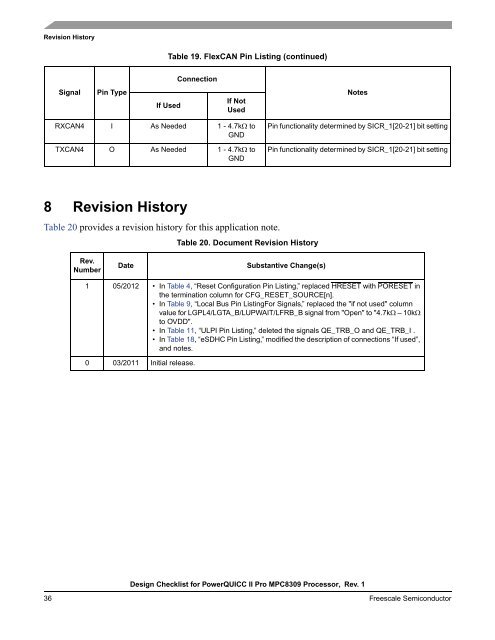

Revision History<br />

Signal Pin Type<br />

RXCAN4 I As Needed 1 - 4.7k� to<br />

GND<br />

TXCAN4 O As Needed 1 - 4.7k� to<br />

GND<br />

8 Revision History<br />

Table 20 provides a revision history <strong>for</strong> this application note.<br />

Rev.<br />

Number<br />

Table 20. Document Revision History<br />

Date Substantive Change(s)<br />

Pin functionality determined by SICR_1[20-21] bit setting<br />

Pin functionality determined by SICR_1[20-21] bit setting<br />

1 05/2012 In Table 4, “Reset Configuration Pin Listing,” replaced HRESET with PORESET in<br />

the termination column <strong>for</strong> CFG_RESET_SOURCE[n].<br />

In Table 9, “Local Bus Pin ListingFor Signals,” replaced the "if not used" column<br />

value <strong>for</strong> LGPL4/LGTA_B/LUPWAIT/LFRB_B signal from "Open" to "4.7k� – 10k��<br />

to OVDD".<br />

In Table 11, “ULPI Pin Listing,” deleted the signals QE_TRB_O and QE_TRB_I .<br />

In Table 18, “eSDHC Pin Listing,” modified the description of connections “If used”,<br />

and notes.<br />

0 03/2011 Initial release.<br />

Table 19. FlexCAN Pin Listing (continued)<br />

If Used<br />

Connection<br />

If Not<br />

Used<br />

<strong>Design</strong> <strong>Checklist</strong> <strong>for</strong> <strong>PowerQUICC</strong> <strong>II</strong> <strong>Pro</strong> <strong>MPC8309</strong> <strong>Pro</strong>cessor, Rev. 1<br />

36 Freescale Semiconductor<br />

Notes