Infineon SAB 80C517A, SAB 83C517A-5 User's Manual ... - Keil

Infineon SAB 80C517A, SAB 83C517A-5 User's Manual ... - Keil

Infineon SAB 80C517A, SAB 83C517A-5 User's Manual ... - Keil

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Semiconductor Group<br />

<strong>80C517A</strong>/<strong>83C517A</strong>-5<br />

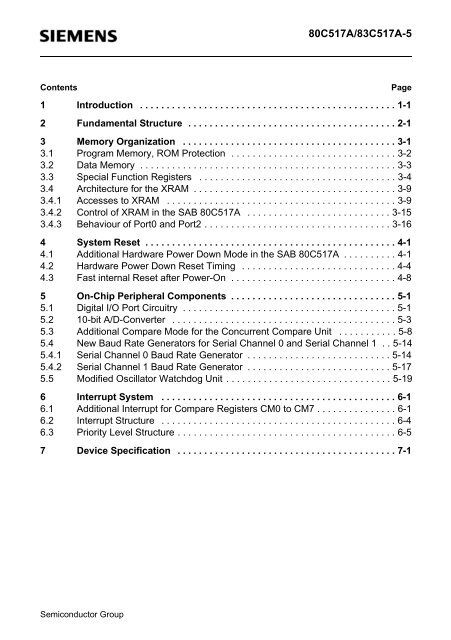

Contents Page<br />

1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1<br />

2 Fundamental Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1<br />

3 Memory Organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1<br />

3.1 Program Memory, ROM Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2<br />

3.2 Data Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3<br />

3.3 Special Function Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4<br />

3.4 Architecture for the XRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9<br />

3.4.1 Accesses to XRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9<br />

3.4.2 Control of XRAM in the <strong>SAB</strong> <strong>80C517A</strong> . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-15<br />

3.4.3 Behaviour of Port0 and Port2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-16<br />

4 System Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1<br />

4.1 Additional Hardware Power Down Mode in the <strong>SAB</strong> <strong>80C517A</strong> . . . . . . . . . . 4-1<br />

4.2 Hardware Power Down Reset Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4<br />

4.3 Fast internal Reset after Power-On . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8<br />

5 On-Chip Peripheral Components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1<br />

5.1 Digital I/O Port Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1<br />

5.2 10-bit A/D-Converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3<br />

5.3 Additional Compare Mode for the Concurrent Compare Unit . . . . . . . . . . . 5-8<br />

5.4 New Baud Rate Generators for Serial Channel 0 and Serial Channel 1 . . 5-14<br />

5.4.1 Serial Channel 0 Baud Rate Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-14<br />

5.4.2 Serial Channel 1 Baud Rate Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-17<br />

5.5 Modified Oscillator Watchdog Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-19<br />

6 Interrupt System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1<br />

6.1 Additional Interrupt for Compare Registers CM0 to CM7 . . . . . . . . . . . . . . . 6-1<br />

6.2 Interrupt Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4<br />

6.3 Priority Level Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5<br />

7 Device Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1