Catálogo 2009 - Pós-Graduação - ITA

Catálogo 2009 - Pós-Graduação - ITA

Catálogo 2009 - Pós-Graduação - ITA

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

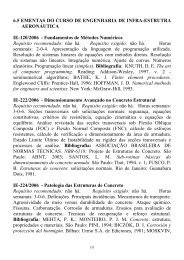

EA-279/<strong>2009</strong> - Arquitetura de Computadores I<br />

Requisito recomendado: EA-266. Requisito exigido: não há. Horas semanais: 3-<br />

1-0-6. Paralelismo em nível de instrução e sua exploração dinâmica. Escalonamento<br />

dinâmico. Emissão múltipla. Paralelismo em nível de thread. Paralelismo em nível de<br />

instrução com abordagens de software. Emissão múltipla estática e arquitetura VLIW.<br />

Mecanismos de especulação de hardware e software. Multiprocessadores e paralelismo<br />

em nível de thread. Multiprocessadores de memória compartilhada simétrica e seu<br />

desempenho. 130 Multiprocessadores de memória compartilhada distribuída e seu<br />

desempenho. Sincronização. Modelos de consistência de memória. Multithreading,<br />

exploração do paralelismo a nível de thread em um processador. Multiprocessador<br />

embutidos. Bibliografia: HENNESSY, J. L. e PATTERSON, D.A., Computer<br />

Architecture: A Quantitative Aproach; 3. ed., Elsevier Science, USA, 2003; JOHNSON,<br />

M., Superscalar Microprocessor Design, Prentice-Hall, Englewood Cliffs, N.J., USA,<br />

1990; Analog Devices - ADSP - BF533 Blackfin Processor Hardware Reference,<br />

Analog Devices Inc., Norwood, Mass. USA, 2003.<br />

EA-281/<strong>2009</strong> - Otimização de Circuitos Digitais<br />

Requisito recomendado: EEA-20. Requisito exigido: não há. Horas semanais: 3-<br />

0-0-6. Características e modelagem de sistemas digitais síncronos: estrutura, técnicas de<br />

particionamento, arquiteturas RTL (Register Transfer Logic), Linguagens de descrição<br />

de circuitos. Otimização e síntese da unidade operadora (dataptah): técnicas de alocação<br />

de unidades funcionais e registradores e técnicas de escalonamento de estados.<br />

Otimização e síntese de máquinas de estado finito síncronas (MEFS): minimização de<br />

estados; assinalamento de estados voltado para redução de área e potência; minimização<br />

lógica de simples saída, múltiplas saídas e multi-nivel; técnicas de eliminação de<br />

glitches; decomposição de máquinas MEFS voltada para redução de potência;<br />

mapeamento tecnológico. Bibliografia: DE MICHELI, G., Synthesis and optimization<br />

of digital circuits, McGraw-Hill1994; VILLA, T., K.A.M, T., BRAYTON, K. R. L.,<br />

SANGIOVANNI-VICENTELLI, A., synthesis of finite state machines: logic<br />

optimization, Kluwer Academic Publishers, 1997; KASTNER, R., KAPLAN, A.,<br />

SARRAFZADEIT, M., Synthesis techniques and optimization fo reconfigurable<br />

systems, Kluwer Academic Publishers 2003.