elektronik-magazin für chip-, board- & system-design - ITwelzel.biz

elektronik-magazin für chip-, board- & system-design - ITwelzel.biz

elektronik-magazin für chip-, board- & system-design - ITwelzel.biz

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Flexible Embedded-Prozessor-Cores <strong>für</strong> PLDs<br />

Neuer Freiheitsgrad <strong>für</strong><br />

Embedded-Designs<br />

Von Altera sind jetzt unter der Produktbezeichnung<br />

»Excalibur« Embedded-Prozessor-Cores <strong>für</strong> flexible<br />

SOPC-Designs (System-On-a-Programmable-<br />

Chip) verfügbar. Mit dem Zugriff auf führende<br />

Prozessorarchitekturen durch Lizenzvereinbarungen<br />

mit MIPS Technologies und ARM sowie der<br />

Entwicklung des firmeneigenen RISC-basierenden<br />

Embedded-Prozessors Nios stehen Lösungen <strong>für</strong><br />

die Systemintegration in programmierbaren Logikbausteinen<br />

bereit. Damit können Entwickler die<br />

engen Time-to-Market-Anforderungen bei geringerem<br />

Risiko und Kosten im Vergleich zu Lösungen<br />

mit ASICs, ASSPs und Standalone-Embedded-Prozessoren<br />

erfüllen.<br />

Der neue Design-Ansatz<br />

kombiniert Programmierbarkeit<br />

mit Logik, Speicher<br />

und Embedded-Prozessoren<br />

auf einem Chip. Für die<br />

erfolgreiche Implementierung<br />

eines kompletten Systems<br />

in einen programmierbaren<br />

Logikbaustein gibt es<br />

dabei einige wesentliche Vorausetzungen:<br />

hochdichte Siliziumprodukte<br />

<strong>für</strong> die Integration<br />

der Hauptfunktionen,<br />

entsprechende Entwicklungs-<br />

Tools, Unterstützung der<br />

Wiederverwendbarkeit im<br />

Design durch IPs mit DSP-,<br />

PCI- oder Embedded-Prozes-<br />

Bild 1. Excalibur vereinigt<br />

programmierbare Logik,<br />

Speicher und Embedded-<br />

Prozessoren <strong>für</strong> Embedded-Systeme-Designs<br />

auf<br />

einem Chip<br />

sor-Funktionalität sowie Partnerschaften<br />

<strong>für</strong> die Bereitstellung<br />

der Design-Infrastruktur.<br />

Die jetzt angebotenen Lösungen<br />

umfassen Embedded-<br />

Prozessor-Architekturen,<br />

Hardware- und Software-Code-Compiler,PLD-Entwicklungs-Tools<br />

sowie Entwicklungs-Hardware.<br />

Um System-Designs<br />

auf Basis von<br />

existierenden Prozessorarchitekturen<br />

unterstützen zu können,<br />

hat Altera den Einsatz<br />

der Prozessorarchitekturen<br />

von ARM und MIPS lizenziert.<br />

Darüber hinaus wurde<br />

bekanntgegeben, dass Altera<br />

mit Motorola entsprechende<br />

Verhandlungen über eine<br />

mögliche Lizenzierung der<br />

PowerPC-Architektur führt.<br />

Diese Lizenzvereinbarungen<br />

erlauben es, führende Prozessor-Cores<br />

auf Transistorebene<br />

zu implementieren und in<br />

PLD-Architekturen von Altera<br />

zu integrieren. Die Vereinbarungen<br />

umfassen auch<br />

alle notwendigen Peripherie-<br />

Cores <strong>für</strong> eine komplette<br />

SOPC-Lösung. Mit diesen<br />

Hardware-Prozessor-Cores<br />

läßt sich eine Performance<br />

von etwa 200 MIPS realisie-<br />

ren. Neben dem eigentlichen<br />

Prozessor-Core sind die<br />

PLDs auch <strong>für</strong> die Implementierung<br />

von On-Chip-RAM,<br />

Cache, externem Bus-Interface<br />

und UART optimiert.<br />

Sind diese On-Chip-Elemente<br />

erstmal implementiert,<br />

dann ist dort die entsprechend<br />

Software ablauffähig und das<br />

Interface zu externen Komponenten<br />

vorhanden, noch<br />

bevor der PLD-Core konfiguriert<br />

wird. Dadurch wird der<br />

Design-Zyklus wesentlich<br />

verkürzt und vereinfacht, indem<br />

Software <strong>für</strong> die Bausteine<br />

noch vor der eigentlichen<br />

PLD-Entwicklung geschrieben<br />

werden kann.<br />

Für eine breite Marktabdeckung,<br />

wo die Kunden nach<br />

einer programmierbaren Lösung<br />

<strong>für</strong> die effiziente und<br />

kosteneffektive Integration eines<br />

flexiblen Embedded-Prozessors<br />

suchen, wurde mit<br />

Nios die erste Embedded-<br />

Prozessorarchitektur <strong>für</strong> programmierbare<br />

Logik entwickelt.<br />

Nios ist ein RISC-basierender,<br />

konfigurierbarer und<br />

skalierbarer Soft-Core-Prozessor<br />

mit 16-Bit-Befehlssatz<br />

und 16-/32-Bit-Datenpfaden.<br />

Implementiert in die APEX<br />

20KE-Architektur kann der<br />

Nios mit 50 MIPS arbeiten<br />

und benötigt etwa 1000 Logikzellen<br />

– das sind etwa zwölf<br />

Prozent eines APEX EP20K-<br />

200E oder zwei Prozent eines<br />

APEX EP20 K1500E.<br />

CHIP-DESIGN<br />

Der Nios-Embedded-Prozessor<br />

kann <strong>für</strong> eine Vielzahl<br />

von Applikationen konfiguriert<br />

werden. So kann ein 16-<br />

Bit-Nios-Core zum Beispiel<br />

ein kleines Programm aus<br />

dem On-Chip-ROM (ESB,<br />

Embedded-System-Block)<br />

ausführen und so einen Sequenzer/Controllerrealisieren,<br />

der eine in Hardware<br />

realisierte State-Machine ersetzen<br />

kann. Ein Nios-Kern<br />

mit 32 Bit und entsprechendem<br />

externen Flash- und<br />

Hauptspeicher erreicht dagegen<br />

eine vergleichbare<br />

Leistung zu einem Standalone-Embedded-Prozessor,<br />

bei größerer Flexibilität.<br />

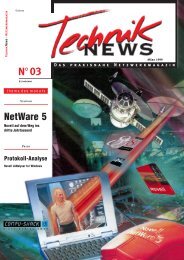

Bild 2. Je nach Applikation bietet die Softcore- oder<br />

Hardcore-Implementierung von Embedded-Prozessoren<br />

Vorteile<br />

Wird eine noch höhere Leistungsfähigkeit<br />

benötigt, dann<br />

können mehrere Nios-Prozessoren<br />

auf einem PLD implementiert<br />

werden.<br />

Über das Altera-Mega-<br />

Wizard-Interface kann ein<br />

Entwickler ein System bezüglich<br />

Speicher und Peripheriefunktionen<br />

einfach<br />

konfigurieren. So können<br />

beispielsweise unterschiedliche<br />

Speicherbreiten- und<br />

-tiefen sowie Peripherietypen<br />

(UART, Timer, PIO,<br />

SRAM- oder Flash-Interface)<br />

ausgewählt werden. Darüber<br />

hinaus kann der Nios<br />

Prozessor-Core auf drei Wegen<br />

erweitert werden:<br />

■ Konventionelle »Memory-Mapped«-Peripheriefunktionen<br />

können auf<br />

Systeme 9/2000 Infos zu Anzeigen/Redaktions-Kennziffern via www.<strong>system</strong>e-online.de/direkt<br />

65