EPP 01.2024

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

» PACKAGING<br />

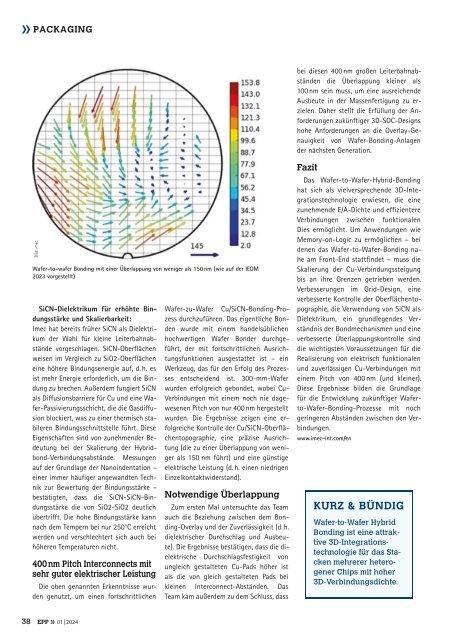

bei diesen 400 nm großen Leiterbahnabständen<br />

die Überlappung kleiner als<br />

100 nm sein muss, um eine ausreichende<br />

Ausbeute in der Massenfertigung zu erzielen.<br />

Daher stellt die Erfüllung der Anforderungen<br />

zukünftiger 3D-SOC-Designs<br />

hohe Anforderungen an die Overlay-Genauigkeit<br />

von Wafer-Bonding-Anlagen<br />

der nächsten Generation.<br />

Bild: imec<br />

Wafer-to-wafer Bonding mit einer Überlappung von weniger als 150 nm (wie auf der IEDM<br />

2023 vorgestellt)<br />

SiCN-Dielektrikum für erhöhte Bindungsstärke<br />

und Skalierbarkeit:<br />

Imec hat bereits früher SiCN als Dielektrikum<br />

der Wahl für kleine Leiterbahnabstände<br />

vorgeschlagen. SiCN-Oberflächen<br />

weisen im Vergleich zu SiO2-Oberflächen<br />

eine höhere Bindungsenergie auf, d. h. es<br />

ist mehr Energie erforderlich, um die Bindung<br />

zu brechen. Außerdem fungiert SiCN<br />

als Diffusionsbarriere für Cu und eine Wafer-Passivierungsschicht,<br />

die die Gasdiffusion<br />

blockiert, was zu einer thermisch stabileren<br />

Bindungsschnittstelle führt. Diese<br />

Eigenschaften sind von zunehmender Bedeutung<br />

bei der Skalierung der Hybridbond-Verbindungsabstände.<br />

Messungen<br />

auf der Grundlage der Nanoindentation –<br />

einer immer häufiger angewandten Technik<br />

zur Bewertung der Bindungsstärke –<br />

bestätigten, dass die SiCN-SiCN-Bindungsstärke<br />

die von SiO2-SiO2 deutlich<br />

übertrifft. Die hohe Bindungsstärke kann<br />

nach dem Tempern bei nur 250°C erreicht<br />

werden und verschlechtert sich auch bei<br />

höheren Temperaturen nicht.<br />

400 nm Pitch Interconnects mit<br />

sehr guter elektrischer Leistung<br />

Die oben genannten Erkenntnisse wurden<br />

genutzt, um einen fortschrittlichen<br />

Wafer-zu-Wafer Cu/SiCN-Bonding-Prozess<br />

durchzuführen. Das eigentliche Bonden<br />

wurde mit einem handelsüblichen<br />

hochwertigen Wafer Bonder durchgeführt,<br />

der mit fortschrittlichen Ausrichtungsfunktionen<br />

ausgestattet ist – ein<br />

Werkzeug, das für den Erfolg des Prozesses<br />

entscheidend ist. 300-mm-Wafer<br />

wurden erfolgreich gebondet, wobei Cu-<br />

Verbindungen mit einem noch nie dagewesenen<br />

Pitch von nur 400 nm hergestellt<br />

wurden. Die Ergebnisse zeigen eine erfolgreiche<br />

Kontrolle der Cu/SiCN-Oberflächentopographie,<br />

eine präzise Ausrichtung<br />

(die zu einer Überlappung von weniger<br />

als 150 nm führt) und eine günstige<br />

elektrische Leistung (d. h. einen niedrigen<br />

Einzelkontaktwiderstand).<br />

Notwendige Überlappung<br />

Zum ersten Mal untersuchte das Team<br />

auch die Beziehung zwischen dem Bonding-Overlay<br />

und der Zuverlässigkeit (d. h.<br />

dielektrischer Durchschlag und Ausbeute).<br />

Die Ergebnisse bestätigen, dass die dielektrische<br />

Durchschlagsfestigkeit von<br />

ungleich gestalteten Cu-Pads höher ist<br />

als die von gleich gestalteten Pads bei<br />

kleinen Interconnect-Abständen. Das<br />

Team kam außerdem zu dem Schluss, dass<br />

Fazit<br />

Das Wafer-to-Wafer-Hybrid-Bonding<br />

hat sich als vielversprechende 3D-Integrationstechnologie<br />

erwiesen, die eine<br />

zunehmende E/A-Dichte und effizientere<br />

Verbindungen zwischen funktionalen<br />

Dies ermöglicht. Um Anwendungen wie<br />

Memory-on-Logic zu ermöglichen – bei<br />

denen das Wafer-to-Wafer-Bonding nahe<br />

am Front-End stattfindet – muss die<br />

Skalierung der Cu-Verbindungssteigung<br />

bis an ihre Grenzen getrieben werden.<br />

Verbesserungen im Grid-Design, eine<br />

verbesserte Kontrolle der Oberflächentopographie,<br />

die Verwendung von SiCN als<br />

Dielektrikum, ein grundlegendes Verständnis<br />

der Bondmechanismen und eine<br />

verbesserte Überlappungskontrolle sind<br />

die wichtigsten Voraussetzungen für die<br />

Realisierung von elektrisch funktionalen<br />

und zuverlässigen Cu-Verbindungen mit<br />

einem Pitch von 400 nm (und kleiner).<br />

Diese Ergebnisse bilden die Grundlage<br />

für die Entwicklung zukünftiger Waferto-Wafer-Bonding-Prozesse<br />

mit noch<br />

geringeren Abständen zwischen den Verbindungen.<br />

www.imec-int.com/en<br />

KURZ & BÜNDIG<br />

Wafer-to-Wafer Hybrid<br />

Bonding ist eine attraktive<br />

3D-Integrationstechnologie<br />

für das Stacken<br />

mehrerer heterogener<br />

Chips mit hoher<br />

3D-Verbindungsdichte.<br />

38 <strong>EPP</strong> » 01 | 2024