Chapter 24 Multichannel Serial Port Interface (McSPI).

Chapter 24 Multichannel Serial Port Interface (McSPI).

Chapter 24 Multichannel Serial Port Interface (McSPI).

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

www.ti.com Functional Description<br />

<strong>24</strong>.3.3.5 Slave Transmit-Only Mode<br />

The slave transmit-only mode is programmable (MCSPI_CH(i)CONF[TRM set to 10). This mode<br />

eliminates the need for the CPU to read the receiver register (minimizing data movement) when only<br />

transmission is meaningful.<br />

To use <strong>McSPI</strong> as a slave transmit-only device with MCSPI_CH(I)CONF[TRM]=10, the user should disable<br />

the RX_full and RX_overflow interrupts and DMA read requests due to the receiver register state.<br />

On completion of SPI word transfer the bit EOT of the register MCSPI_CH(I)STAT is set. This bit is<br />

meaningless when using the Buffer for this channel.<br />

The built-in FIFO is available in this mode and can be configured with FFER bit field in the<br />

MCSPI_CH(I)CONF register, then the FIFO is seen as a unique FFNBYTE bytes buffer.<br />

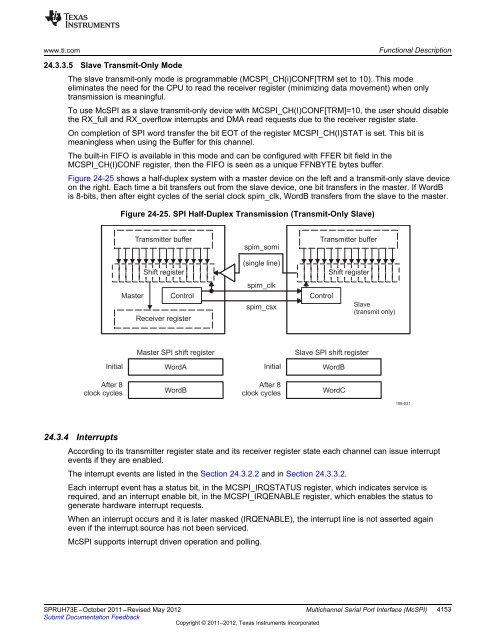

Figure <strong>24</strong>-25 shows a half-duplex system with a master device on the left and a transmit-only slave device<br />

on the right. Each time a bit transfers out from the slave device, one bit transfers in the master. If WordB<br />

is 8-bits, then after eight cycles of the serial clock spim_clk, WordB transfers from the slave to the master.<br />

Initial<br />

After 8<br />

clock cycles<br />

<strong>24</strong>.3.4 Interrupts<br />

Figure <strong>24</strong>-25. SPI Half-Duplex Transmission (Transmit-Only Slave)<br />

Transmitter buffer<br />

Shift register<br />

Master Control<br />

Receiver register<br />

Master SPI shift register<br />

WordA<br />

WordB<br />

spim_somi<br />

(single line)<br />

spim_clk<br />

spim_csx<br />

Initial<br />

After 8<br />

clock cycles<br />

Transmitter buffer<br />

Control<br />

Shift register<br />

Slave SPI shift register<br />

WordB<br />

WordC<br />

Slave<br />

(transmit only)<br />

According to its transmitter register state and its receiver register state each channel can issue interrupt<br />

events if they are enabled.<br />

The interrupt events are listed in the Section <strong>24</strong>.3.2.2 and in Section <strong>24</strong>.3.3.2.<br />

Each interrupt event has a status bit, in the MCSPI_IRQSTATUS register, which indicates service is<br />

required, and an interrupt enable bit, in the MCSPI_IRQENABLE register, which enables the status to<br />

generate hardware interrupt requests.<br />

When an interrupt occurs and it is later masked (IRQENABLE), the interrupt line is not asserted again<br />

even if the interrupt source has not been serviced.<br />

<strong>McSPI</strong> supports interrupt driven operation and polling.<br />

SPRUH73E–October 2011–Revised May 2012 <strong>Multichannel</strong> <strong>Serial</strong> <strong>Port</strong> <strong>Interface</strong> (<strong>McSPI</strong>)<br />

Submit Documentation Feedback<br />

Copyright © 2011–2012, Texas Instruments Incorporated<br />

108-031<br />

4153