Design and Implementation of TinyGALS: A Programming Model for ...

Design and Implementation of TinyGALS: A Programming Model for ...

Design and Implementation of TinyGALS: A Programming Model for ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

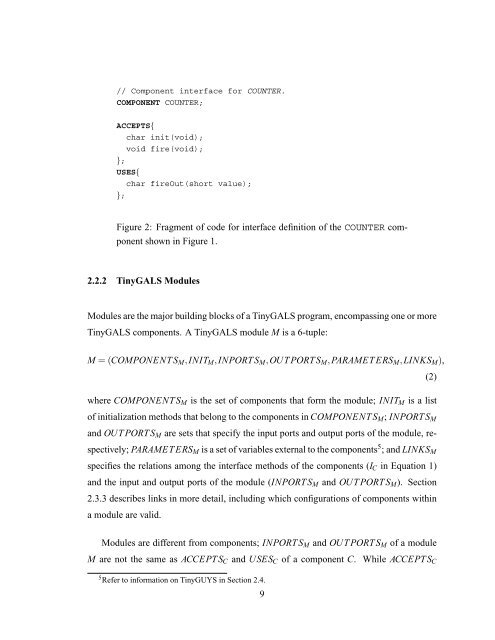

Component interface <strong>for</strong> COUNTER.<br />

COMPONENT COUNTER;<br />

ACCEPTS{<br />

char init(void);<br />

void fire(void);<br />

};<br />

USES{<br />

char fireOut(short value);<br />

};<br />

Figure 2: Fragment <strong>of</strong> code <strong>for</strong> interface definition <strong>of</strong> the COUNTER com-<br />

ponent shown in Figure 1.<br />

2.2.2 <strong>TinyGALS</strong> Modules<br />

Modules are the major building blocks <strong>of</strong> a <strong>TinyGALS</strong> program, encompassing one or more<br />

<strong>TinyGALS</strong> components. A <strong>TinyGALS</strong> module M is a 6-tuple:<br />

M = (COMPONENT SM,INITM,INPORT SM,OUT PORT SM,PARAMET ERSM,LINKSM),<br />

where COMPONENT SM is the set <strong>of</strong> components that <strong>for</strong>m the module; INITM is a list<br />

<strong>of</strong> initialization methods that belong to the components in COMPONENT SM; INPORT SM<br />

<strong>and</strong> OUT PORT SM are sets that specify the input ports <strong>and</strong> output ports <strong>of</strong> the module, re-<br />

spectively; PARAMET ERSM is a set <strong>of</strong> variables external to the components 5 ; <strong>and</strong> LINKSM<br />

specifies the relations among the interface methods <strong>of</strong> the components (IC in Equation 1)<br />

<strong>and</strong> the input <strong>and</strong> output ports <strong>of</strong> the module (INPORT SM <strong>and</strong> OUT PORT SM). Section<br />

2.3.3 describes links in more detail, including which configurations <strong>of</strong> components within<br />

a module are valid.<br />

Modules are different from components; INPORT SM <strong>and</strong> OUT PORT SM <strong>of</strong> a module<br />

M are not the same as ACCEPT SC <strong>and</strong> USESC <strong>of</strong> a component C. While ACCEPT SC<br />

5 Refer to in<strong>for</strong>mation on TinyGUYS in Section 2.4.<br />

9<br />

(2)