Design and Implementation of TinyGALS: A Programming Model for ...

Design and Implementation of TinyGALS: A Programming Model for ...

Design and Implementation of TinyGALS: A Programming Model for ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

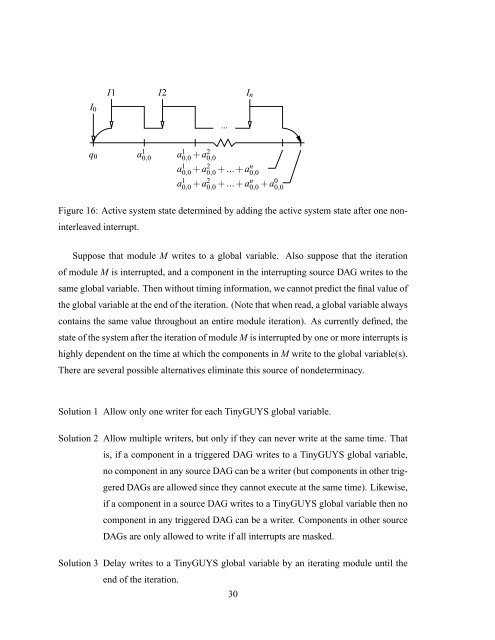

I0<br />

q0<br />

I1 I2 In<br />

a 1 0,0<br />

a 1 0,0 + a2 0,0<br />

...<br />

a 1 0,0 + a2 0,0 + ... + an 0,0<br />

a 1 0,0 + a2 0,0 + ... + an 0,0 + a0 0,0<br />

Figure 16: Active system state determined by adding the active system state after one non-<br />

interleaved interrupt.<br />

Suppose that module M writes to a global variable. Also suppose that the iteration<br />

<strong>of</strong> module M is interrupted, <strong>and</strong> a component in the interrupting source DAG writes to the<br />

same global variable. Then without timing in<strong>for</strong>mation, we cannot predict the final value <strong>of</strong><br />

the global variable at the end <strong>of</strong> the iteration. (Note that when read, a global variable always<br />

contains the same value throughout an entire module iteration). As currently defined, the<br />

state <strong>of</strong> the system after the iteration <strong>of</strong> module M is interrupted by one or more interrupts is<br />

highly dependent on the time at which the components in M write to the global variable(s).<br />

There are several possible alternatives eliminate this source <strong>of</strong> nondeterminacy.<br />

Solution 1 Allow only one writer <strong>for</strong> each TinyGUYS global variable.<br />

Solution 2 Allow multiple writers, but only if they can never write at the same time. That<br />

is, if a component in a triggered DAG writes to a TinyGUYS global variable,<br />

no component in any source DAG can be a writer (but components in other trig-<br />

gered DAGs are allowed since they cannot execute at the same time). Likewise,<br />

if a component in a source DAG writes to a TinyGUYS global variable then no<br />

component in any triggered DAG can be a writer. Components in other source<br />

DAGs are only allowed to write if all interrupts are masked.<br />

Solution 3 Delay writes to a TinyGUYS global variable by an iterating module until the<br />

end <strong>of</strong> the iteration.<br />

30