Design and Implementation of TinyGALS: A Programming Model for ...

Design and Implementation of TinyGALS: A Programming Model for ...

Design and Implementation of TinyGALS: A Programming Model for ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Determinacy <strong>of</strong> a system without global variables. We will first examine the case<br />

where there are no TinyGUYS global variables.<br />

Let us consider a module M that contains a component C which produces events on<br />

the outports <strong>of</strong> M. Suppose the iteration <strong>of</strong> module M is interrupted one or more times.<br />

Since source DAGs must not be connected to triggered DAGs, the interrupt(s) cannot cause<br />

the production <strong>of</strong> events on outports <strong>of</strong> M that would be used in the case <strong>of</strong> a normal<br />

uninterrupted iteration. However, the interrupt(s) may cause insertion <strong>of</strong> events into other<br />

module inport queues, <strong>and</strong> hence insertions into the global event queue. Depending on the<br />

relative timing between the interrupts <strong>and</strong> the production <strong>of</strong> events by C at outports <strong>of</strong> M,<br />

the order <strong>of</strong> events in the global event queue may not be consistent between multiple runs<br />

<strong>of</strong> the system if the same interrupts occur during the same module iteration, but at slightly<br />

different times. This is a source <strong>of</strong> non-determinacy.<br />

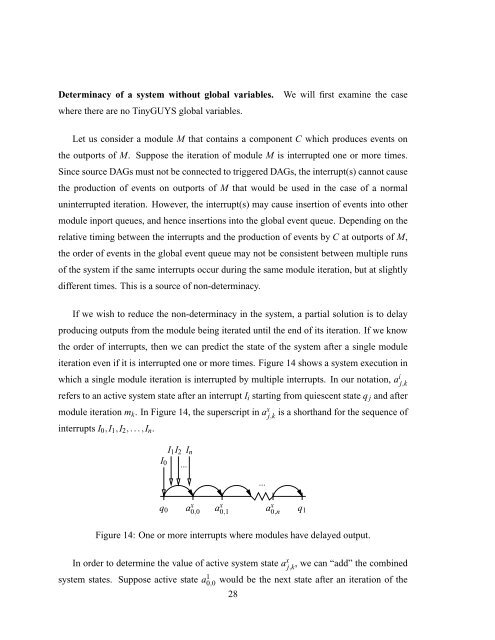

If we wish to reduce the non-determinacy in the system, a partial solution is to delay<br />

producing outputs from the module being iterated until the end <strong>of</strong> its iteration. If we know<br />

the order <strong>of</strong> interrupts, then we can predict the state <strong>of</strong> the system after a single module<br />

iteration even if it is interrupted one or more times. Figure 14 shows a system execution in<br />

which a single module iteration is interrupted by multiple interrupts. In our notation, a i j,k<br />

refers to an active system state after an interrupt Ii starting from quiescent state q j <strong>and</strong> after<br />

module iteration mk. In Figure 14, the superscript in ax j,k is a shorth<strong>and</strong> <strong>for</strong> the sequence <strong>of</strong><br />

interrupts I0,I1,I2,...,In.<br />

I0<br />

q0<br />

I1I2 In<br />

...<br />

a x 0,0<br />

a x 0,1<br />

...<br />

a x 0,n<br />

Figure 14: One or more interrupts where modules have delayed output.<br />

In order to determine the value <strong>of</strong> active system state ax j,k , we can “add” the combined<br />

system states. Suppose active state a1 0,0 would be the next state after an iteration <strong>of</strong> the<br />

28<br />

q1