- Page 1 and 2:

Instruction Set Nomenclature: Statu

- Page 3 and 4:

Conditional Branch Summary Instruct

- Page 5 and 6:

Instruction Set Summary (Continued)

- Page 7 and 8:

Instruction Set Summary (Continued)

- Page 9 and 10:

ADC - Add with Carry Description: A

- Page 11 and 12:

ADIW - Add Immediate to Word Instru

- Page 13 and 14:

ANDI - Logical AND with Immediate I

- Page 15 and 16:

BCLR - Bit Clear in SREG Descriptio

- Page 17 and 18:

BRBC - Branch if Bit in SREG is Cle

- Page 19 and 20:

BRCC - Branch if Carry Cleared Inst

- Page 21 and 22:

BREQ - Branch if Equal Instruction

- Page 23 and 24:

BRHC - Branch if Half Carry Flag is

- Page 25 and 26:

BRID - Branch if Global Interrupt i

- Page 27 and 28:

BRLO - Branch if Lower (Unsigned) I

- Page 29 and 30:

BRMI - Branch if Minus Instruction

- Page 31 and 32:

BRPL - Branch if Plus Instruction S

- Page 33 and 34:

BRTC - Branch if the T Flag is Clea

- Page 35 and 36:

BRVC - Branch if Overflow Cleared I

- Page 37 and 38:

BSET - Bit Set in SREG Description:

- Page 39 and 40:

CALL - Long Call to a Subroutine In

- Page 41 and 42:

CBR - Clear Bits in Register Instru

- Page 43 and 44:

CLH - Clear Half Carry Flag Descrip

- Page 45 and 46:

CLN - Clear Negative Flag Descripti

- Page 47 and 48:

CLS - Clear Signed Flag Description

- Page 49 and 50:

CLV - Clear Overflow Flag Descripti

- Page 51 and 52:

COM - One’s Complement Descriptio

- Page 53 and 54:

CPC - Compare with Carry Instructio

- Page 55 and 56:

CPSE - Compare Skip if Equal Instru

- Page 57 and 58:

EICALL - Extended Indirect Call to

- Page 59 and 60:

ELPM - Extended Load Program Memory

- Page 61 and 62:

ESPM - Extended Store Program Memor

- Page 63 and 64:

FMUL - Fractional Multiply Unsigned

- Page 65 and 66:

FMULSU - Fractional Multiply Signed

- Page 67 and 68:

IJMP - Indirect Jump Instruction Se

- Page 69 and 70:

INC - Increment Instruction Set Des

- Page 71 and 72: LD - Load Indirect from data space

- Page 73 and 74: LD (LDD) - Load Indirect from data

- Page 75 and 76: LD (LDD) - Load Indirect From data

- Page 77 and 78: LDI - Load Immediate Description: L

- Page 79 and 80: LPM - Load Program Memory Instructi

- Page 81 and 82: LSR - Logical Shift Right Instructi

- Page 83 and 84: MOVW - Copy Register Word Instructi

- Page 85 and 86: MULS - Multiply Signed Description:

- Page 87 and 88: NEG - Two’s Complement Descriptio

- Page 89 and 90: OR - Logical OR Instruction Set Des

- Page 91 and 92: OUT - Store Register to I/O Locatio

- Page 93 and 94: PUSH - Push Register on Stack Instr

- Page 95 and 96: RET - Return from Subroutine Instru

- Page 97 and 98: RJMP - Relative Jump Instruction Se

- Page 99 and 100: ROR - Rotate Right through Carry In

- Page 101 and 102: SBC - Subtract with Carry Instructi

- Page 103 and 104: SBI - Set Bit in I/O Register Instr

- Page 105 and 106: SBIS - Skip if Bit in I/O Register

- Page 107 and 108: SBR - Set Bits in Register Instruct

- Page 109 and 110: SBRS - Skip if Bit in Register is S

- Page 111 and 112: SEH - Set Half Carry Flag Descripti

- Page 113 and 114: SEN - Set Negative Flag Description

- Page 115 and 116: SES - Set Signed Flag Description:

- Page 117 and 118: SEV - Set Overflow Flag Description

- Page 119 and 120: SLEEP Description: This instruction

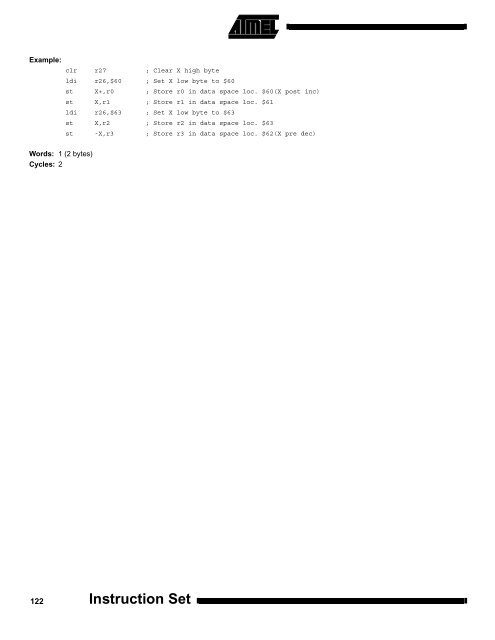

- Page 121: ST - Store Indirect From Register t

- Page 125 and 126: ST (STD) - Store Indirect From Regi

- Page 127 and 128: STS - Store Direct to data space In

- Page 129 and 130: SUBI - Subtract Immediate Instructi

- Page 131 and 132: TST - Test for Zero or Minus Instru

- Page 133: Atmel Headquarters Atmel Operations