Elektronika 2010-11.pdf - Instytut Systemów Elektronicznych ...

Elektronika 2010-11.pdf - Instytut Systemów Elektronicznych ...

Elektronika 2010-11.pdf - Instytut Systemów Elektronicznych ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Fig. 4. CSA characteristics and output pulse shapes<br />

Rys. 4. Charakterystyki i impulsy wyjściowe ze wzmacniacza ładunkowego<br />

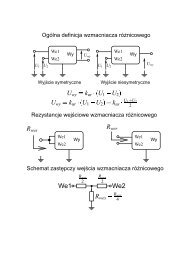

B. Discriminator<br />

The task of the discriminator is to produce an output pulse<br />

lasting as long as the CSA output exceeds certain voltage level,<br />

called the threshold. The presented architecture consists<br />

of several blocks (Fig. 5).<br />

The first stage is the unary-gain differential amplifier<br />

(M 1<br />

–M 4<br />

). Its main task is to convert the single-ended CSA<br />

output signal into fully differential one in order to keep the<br />

operation of the next stage (actual discriminator) most effective.<br />

Additionally, this stage implements both differential<br />

threshold setting (pins Th1 and Th2) and the trimming functionality<br />

(DAC pin). The fully differential discriminator with<br />

hysteresis (M 5<br />

– M 10<br />

) has been described in details by P. Allen<br />

[9]. The transistors are sized to reach the high gain. The<br />

complex, cross-coupled load structure (M 7<br />

– M 10<br />

) introduces<br />

the hysteresis which prevents the multiple, short discriminator<br />

pulses resulting from the noise. M 11<br />

– M 14<br />

transistors provide<br />

the full swing output and increase the overall gain of the<br />

discriminator. In order to uniform the output pulse polarity no<br />

matter what is the polarization of the input charge, the pulse<br />

is inverted or buffered depending on the actual polarity line<br />

configuration.<br />

C. TrimDAC<br />

The purpose of the 6-bit, constant-current architecture Trim-<br />

DAC is to compensate for the CSA output DC level deviation<br />

(Fig. 6). Since the threshold is set globally for all the channels,<br />

the deviation changes the effective threshold setting. The reference<br />

currents for the DAC are to be set externally for both<br />

range and offset. The register supports the initialization to the<br />

default value which is equal to the half of the full range. The<br />

common-centroid layout has been used. The presented circuit<br />

keeps the linearity in the operation range and offset values<br />

exceeding the expected ones (resulting from the monte-carlo<br />

analysis).<br />

Fig. 5. Architecture of the discriminator Rys. 5. Architektura dyskryminatora<br />

Fig. 6. Simplified TrimDAC architecture (register, decoder and references are not included)<br />

Rys. 6. Uproszczony schemat układu TrimDAC (rejestr, dekoder oraz obwody referencyjne są pominięte)<br />

<strong>Elektronika</strong> 11/<strong>2010</strong> 21