Elektronika 2010-11.pdf - Instytut Systemów Elektronicznych ...

Elektronika 2010-11.pdf - Instytut Systemów Elektronicznych ...

Elektronika 2010-11.pdf - Instytut Systemów Elektronicznych ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

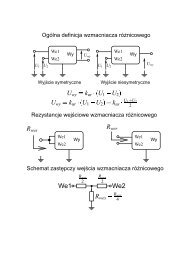

Fig. 6. Architecture of a VLSI circuit implementing a fuzzy logic controller based on interval typ-2 fuzzy sets<br />

Rys. 6. Architektura układu VLSI realizującego sterownik rozmyty oparty na interwałowych zbiorach rozmytych 2-go rzędu<br />

and compute the component grades for all the elements<br />

in the universe of discourse. Taking the next<br />

rule causes the resulting membership function of<br />

the output fuzzy set to be updated. This kind of<br />

processing allows to save up to 2*i*n i *2 r switches<br />

in the circuit, where i, n and r are the numbers<br />

of inputs, input fuzzy sets and accuracy bits, respectively.<br />

The algorithms of type reduction and defuzzification,<br />

mentioned in the previous section, were<br />

implemented as a one module since they are essentially<br />

based on the same set of operations and<br />

therefore share the same building blocks: adders,<br />

multiplication and division circuits. The aim of type<br />

reduction is to map the output interval type-2 fuzzy<br />

set, obtained in the inference module, into a classical<br />

interval fuzzy set. The iterative KM algorithm has to be<br />

executed twice per each output to find the left y L<br />

and the right<br />

y R<br />

bounds of the output interval type-1 set. The ΣΠ and Σ blocks<br />

compute iteratively the numerator and denominator of (6),<br />

respectively. After that, the result of division is stored in the<br />

register, selected by the FSM depending on the stage of algorithm.<br />

At the end of each pass of algorithm, one of the output<br />

registers R L<br />

or R R<br />

is loaded with the appropriate value of y L<br />

or<br />

y R<br />

bound, respectively. The crisp output value is finally computed<br />

in the Σ/2 block as their arithmetic mean.<br />

Experimental results<br />

The proposed type-2 FLC circuit was implemented in the<br />

standard cells approach using CMOS 90 nm technology. The<br />

VHDL model is highly parameterized which means, that depending<br />

on purpose, one can specify: the number of input and<br />

output signals, the number of input and output fuzzy sets, the<br />

type of fuzzy sets (singleton, triangle, trapezoid) and finally the<br />

number of accuracy bits.<br />

Tabl. 1. Design parameters of the FLC circuit in CMOS 90 nm technology<br />

Tab. 1. Parametry układu FLC w technologii CMOS 90 nm<br />

No of<br />

inputs<br />

No of<br />

outputs<br />

No of input<br />

fuzzy<br />

sets<br />

Tabl. 2. Comparison of the parameters of the FLC circuits<br />

Tab. 2. Porównanie parametrów układów FLC<br />

Circuit<br />

No of output<br />

fuzzy<br />

sets<br />

No of cells<br />

Accuracy<br />

Core area<br />

[μm 2 ]<br />

Processing speed<br />

[MFLIPS]<br />

pipelined FLC [4] 470 000 3.125<br />

our FLC 20 000 0.280<br />

Power<br />

[mW]<br />

4 2 4 4 4 38586 0.98<br />

2 4 4 4 4 37230 1.04<br />

4 4 4 4 4 47211 1.19<br />

2 2 4 4 4 28631 0.82<br />

2 2 4 8 4 28631 0.83<br />

2 2 4 4 8 319715 10.16<br />

2 2 8 4 8 319888 10.13<br />

Several experiments with various sets of parameters were<br />

performed in order to check their influence on the area and<br />

power consumption of the FLC circuit. The examples were<br />

chosen in part from practical control applications and reflect<br />

their typical complexity. The circuits were synthesized and<br />

then simulated with the timing parameters of standard cells<br />

from the library.<br />

The results of synthesis and simulation let us estimate the<br />

major parameters of the circuits, which are summarized in<br />

Table 1. The biggest influence on circuit size and power has<br />

the number of accuracy bits, as the sizes of all building blocks<br />

<strong>Elektronika</strong> 11/<strong>2010</strong> 47