Elektronika 2010-11.pdf - Instytut Systemów Elektronicznych ...

Elektronika 2010-11.pdf - Instytut Systemów Elektronicznych ...

Elektronika 2010-11.pdf - Instytut Systemów Elektronicznych ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

The design of low power 11.6 mW high speed 1.8 Gb/s<br />

stand-alone LVDS Driver in 0.18 µm CMOS<br />

(Projekt scalonego nadajnika standardu LVDS o niskim poborze mocy 11,6 mW<br />

i 1,8 Gb/s szybkości transmisji danych)<br />

mgr inż. RAFAŁ KŁECZEK, Akademia Górniczo-Hutnicza, Katedra Metrologii, Kraków<br />

According to Moore’s law CMOS technology has been exponentially<br />

developed over the several recent decades. This development<br />

is particularly visible in digital part where reducing<br />

the effective channel’s length is equivalent to increasing the<br />

frequency of circuits. Growth in the performance of microprocessor<br />

motherboards, optical transmission links, chip-to-chip<br />

communications has created a higher and higher speed requirements<br />

on physical layer interfaces. Due to limited performance<br />

of single link high data rates were achieved by parallelism<br />

in the past, that increased the complexity level and cost<br />

of the fabricated circuits. Nowadays data rates at the range<br />

of few hundred MHz up to or above is necessary. Reducing<br />

the power dissipation is very often one of the most critical modern<br />

circuits’ requirements.<br />

LVDS (Low Voltage Differential Signaling) standard offers<br />

high speed data transmission and low power consumption<br />

at the same time. Due to many advantages of differential<br />

operation: robustness of the link to supply lines and common<br />

mode voltage bouncing, reduction of coupling and radiated<br />

electro-magnetic interference (EMI), higher level of electromagnetic<br />

compatibility (EMC) [1–2] in conjunction with low<br />

voltage swing has become a popular choice for fast data onchip<br />

transmission, on board/backplane or cable connections.<br />

The benefits of LVDS make it valuable technology, that fits<br />

into a wide range of applications such as: PC/computing, telecommunication,<br />

automotive, etc. [3].<br />

This paper presents the design of low-power complete<br />

stand-alone LVDS driver in 180-nm CMOS technology.<br />

It offers a dense packing of transistors and implementation<br />

of mixed-mode circuits. It also occupies low area so makes<br />

the driver suitable for using in multichannel ASIC.<br />

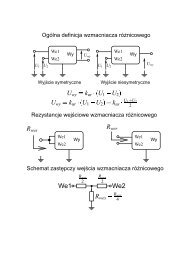

LVDS Interface<br />

LVDS standard was specified by IEEE as a norm that based<br />

on the physical layer defined for the scalable coherent interface<br />

(SCI) [4] (separate industry standard was defined by TIA-<br />

EIA [5]). It specifies the dc and ac parameters for driver and<br />

receiver shown in Fig. 1.<br />

The most important of them are: differential voltage<br />

(V DIFF<br />

= V oa<br />

– V ob<br />

) and common mode voltage V CM<br />

= (V oa<br />

+ V ob<br />

)/2.<br />

A differential voltage is centered at a common mode voltage.<br />

Regarding a value of termination resistor R R<br />

and process, voltage,<br />

temperature (PVT) variations the ranges of this voltages<br />

are defined as:<br />

250 mV ≤ |V DIFF<br />

| ≤ 400 mV (1)<br />

1.125 V ≤ V CM<br />

≤ 1.275 V (2)<br />

For simplicity LVDS transmitter can be considered as current<br />

source with switched polarity, whereas the receiver is a comparator<br />

with hysteresis which can detect voltage signal at the<br />

level of tens of mV. The driver’s output current I D<br />

= 3.6 mA<br />

flows through differential pair lines and termination resistor<br />

R R<br />

= 100 Ω (in most cases R R<br />

= 2R L<br />

, R L<br />

is characteristic impedance<br />

of transmission line). The receiver has a high DC input<br />

impedance so the majority of driver’s output current flows<br />

across R R<br />

resistor and generates at the receiver input about<br />

360 mV, which can be detect as “one” logic state. Switching<br />

driver’s current polarity changes flow direction across R R<br />

resistor,<br />

thereby creating a valid “one” or “zero” logic state.<br />

LVDS Transmitter<br />

A stand-alone LVDS driver can be constructed of the following<br />

functional blocks (Fig. 2):<br />

• LVDS core: current source with switched polarity,<br />

• CMFB: common mode feedback circuit stabilizes the<br />

driver’s output common mode voltage V CM<br />

at the desired<br />

value, which equals V REF<br />

. Output’s voltage V CM<br />

is probed<br />

by resistive divider made of R P<br />

resistors.<br />

• Control block: block responsible for controlling the LVDS<br />

core, it buffers the input signal U DATA<br />

.<br />

• Band-gap: generates a V REF<br />

reference voltage, which should<br />

have no temperature dependence.<br />

During the simulation the receiver was modeled as a parallel<br />

combination of termination resistor R R<br />

= 100 Ω and capa-<br />

Fig. 1. Components of LVDS interface [4]<br />

Rys. 1. Elementy składowe interfejsu LVDS [4]<br />

Fig. 2. Block diagram of LVDS driver<br />

Rys. 2. Schemat blokowy nadajnika standardu<br />

<strong>Elektronika</strong> 11/<strong>2010</strong> 23