SC16IS740/750/760 Single UART with I2C-bus/SPI interface, 64 ...

SC16IS740/750/760 Single UART with I2C-bus/SPI interface, 64 ...

SC16IS740/750/760 Single UART with I2C-bus/SPI interface, 64 ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

NXP Semiconductors<br />

<strong>SC16IS740</strong>/<strong>750</strong>/<strong>760</strong><br />

<strong>Single</strong> <strong>UART</strong> <strong>with</strong> I 2 C-<strong>bus</strong>/<strong>SPI</strong> <strong>interface</strong>, <strong>64</strong>-byte FIFOs, IrDA SIR<br />

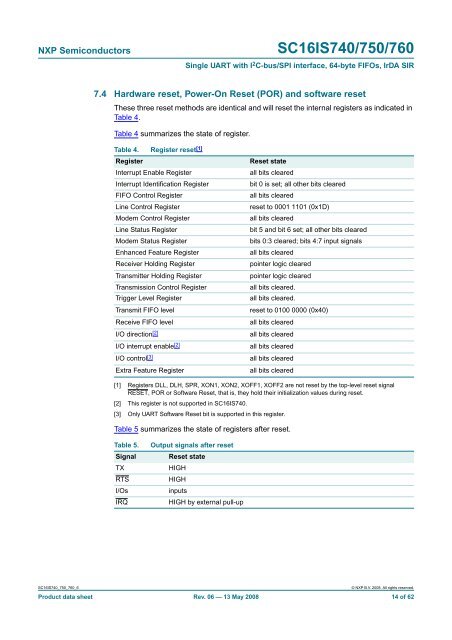

7.4 Hardware reset, Power-On Reset (POR) and software reset<br />

These three reset methods are identical and will reset the internal registers as indicated in<br />

Table 4.<br />

Table 4 summarizes the state of register.<br />

Table 4. Register reset [1]<br />

Register<br />

Interrupt Enable Register<br />

Interrupt Identification Register<br />

FIFO Control Register<br />

Line Control Register<br />

Modem Control Register<br />

Line Status Register<br />

Modem Status Register<br />

Enhanced Feature Register<br />

Receiver Holding Register<br />

Transmitter Holding Register<br />

Transmission Control Register<br />

Trigger Level Register<br />

Transmit FIFO level<br />

Receive FIFO level<br />

I/O direction [2]<br />

I/O interrupt enable [2]<br />

I/O control [3]<br />

Extra Feature Register<br />

Reset state<br />

all bits cleared<br />

bit 0 is set; all other bits cleared<br />

all bits cleared<br />

reset to 0001 1101 (0x1D)<br />

all bits cleared<br />

bit 5 and bit 6 set; all other bits cleared<br />

bits 0:3 cleared; bits 4:7 input signals<br />

all bits cleared<br />

pointer logic cleared<br />

pointer logic cleared<br />

all bits cleared.<br />

all bits cleared.<br />

reset to 0100 0000 (0x40)<br />

all bits cleared<br />

all bits cleared<br />

all bits cleared<br />

all bits cleared<br />

all bits cleared<br />

[1] Registers DLL, DLH, SPR, XON1, XON2, XOFF1, XOFF2 are not reset by the top-level reset signal<br />

RESET, POR or Software Reset, that is, they hold their initialization values during reset.<br />

[2] This register is not supported in <strong>SC16IS740</strong>.<br />

[3] Only <strong>UART</strong> Software Reset bit is supported in this register.<br />

Table 5 summarizes the state of registers after reset.<br />

Table 5.<br />

Signal<br />

TX<br />

RTS<br />

I/Os<br />

IRQ<br />

Output signals after reset<br />

Reset state<br />

HIGH<br />

HIGH<br />

inputs<br />

HIGH by external pull-up<br />

<strong>SC16IS740</strong>_<strong>750</strong>_<strong>760</strong>_6<br />

© NXP B.V. 2008. All rights reserved.<br />

Product data sheet Rev. 06 — 13 May 2008 14 of 62