SC16IS740/750/760 Single UART with I2C-bus/SPI interface, 64 ...

SC16IS740/750/760 Single UART with I2C-bus/SPI interface, 64 ...

SC16IS740/750/760 Single UART with I2C-bus/SPI interface, 64 ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

NXP Semiconductors<br />

<strong>SC16IS740</strong>/<strong>750</strong>/<strong>760</strong><br />

<strong>Single</strong> <strong>UART</strong> <strong>with</strong> I 2 C-<strong>bus</strong>/<strong>SPI</strong> <strong>interface</strong>, <strong>64</strong>-byte FIFOs, IrDA SIR<br />

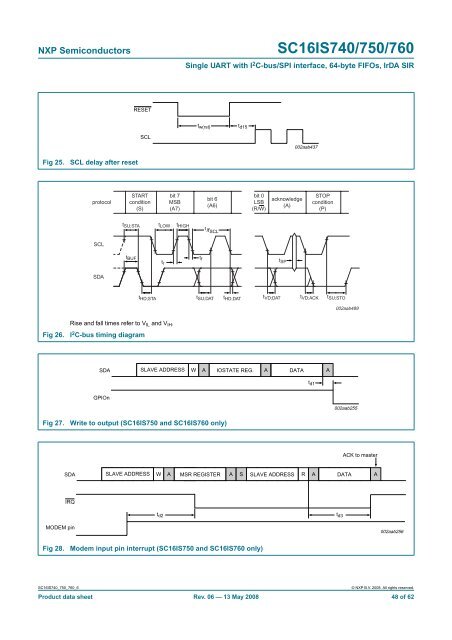

RESET<br />

t w(rst)<br />

t d15<br />

SCL<br />

002aab437<br />

Fig 25.<br />

SCL delay after reset<br />

protocol<br />

START<br />

condition<br />

(S)<br />

bit 7<br />

MSB<br />

(A7)<br />

bit 6<br />

(A6)<br />

bit 0<br />

LSB<br />

(R/W)<br />

acknowledge<br />

(A)<br />

STOP<br />

condition<br />

(P)<br />

1 /f SCL<br />

SCL<br />

SDA<br />

t t LOW t HIGH<br />

t VD;ACK<br />

t BUF<br />

t r<br />

t f<br />

t HD;STA t SU;DAT t HD;DAT<br />

SU;STA<br />

002aab489<br />

t VD;DAT<br />

t SP<br />

t SU;STO<br />

Fig 26.<br />

Rise and fall times refer to V IL and V IH .<br />

I 2 C-<strong>bus</strong> timing diagram<br />

SDA<br />

SLAVE ADDRESS<br />

W<br />

A<br />

AIOSTATE REG.<br />

A<br />

DATA<br />

A<br />

t d1<br />

GPIOn<br />

002aab255<br />

Fig 27.<br />

Write to output (SC16IS<strong>750</strong> and SC16IS<strong>760</strong> only)<br />

ACK to master<br />

SDA SLAVE ADDRESS W A AMSR REGISTER A S SLAVE ADDRESS R A DATA A<br />

IRQ<br />

t d2 t d3<br />

MODEM pin<br />

002aab256<br />

Fig 28.<br />

Modem input pin interrupt (SC16IS<strong>750</strong> and SC16IS<strong>760</strong> only)<br />

<strong>SC16IS740</strong>_<strong>750</strong>_<strong>760</strong>_6<br />

© NXP B.V. 2008. All rights reserved.<br />

Product data sheet Rev. 06 — 13 May 2008 48 of 62