industry news - Chip Scale Review

industry news - Chip Scale Review

industry news - Chip Scale Review

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

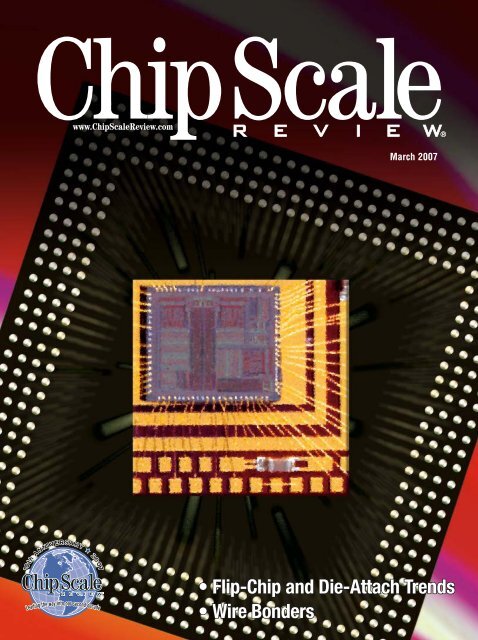

<strong>Chip</strong><strong>Scale</strong>®<br />

www.<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com<br />

r e v i e w<br />

March 2007<br />

• Flip-<strong>Chip</strong> and Die-Attach Trends<br />

• Wire Bonders

One Stop Wafer Bumping & WLCSP with UAT<br />

Wafer Level <strong>Chip</strong>scale Package<br />

Wafer Bumping Services<br />

Gold Bumps<br />

Bump Height typically ranges from 2 to 25 microns and bump pitch may go as<br />

low as 35 micons<br />

Copper Pillar Bumps<br />

Copper pillar bumps with solder cap of either SnAg or pure Sn for fine pitch<br />

application. Bump pitch may go as low as 100 microns. Typical bump height is<br />

65 microns of copper pillar with 20 microns of solder cap.<br />

Small Solder Bumps<br />

Electroplated solder bumps either of SnAg or pure Sn fr fine pitch application.<br />

Bump height typically ranges between 25 to 100 microns. Bump pitch may go<br />

as low as 100 microns for lower bump heights.<br />

Large Solder Bumps<br />

Ball drop and ‘reflow’ bump height ranges between 150 to 350 microns<br />

depending on diameter or Under-bump metallization and solder ball size being<br />

used. Typical solder bump composition is SnAgCu (3.0% Ag and 0.5% Cu)<br />

Repassivation & pad redistribution<br />

Polymide or Bensocyclobutene as the repassivation layer for enhancing the<br />

performance and reliability of wafer-level packaging redistribution of bond pads<br />

into matric arrays to cater for devices not currently designed for wafer bumping.<br />

• Backgrind<br />

• Laser Mask<br />

• Test<br />

• Singulation<br />

• Inspection<br />

• Tape & Reel<br />

• Qualification Reports<br />

available at this time<br />

Unisem-Advanpack Technologies Sdn Bhd (*UAT*), a joint venture between Unisem (M) Berhad (“Unsiem”) and Advanpack<br />

Solutions Pte Ltd., located in Ipoh, Malaysia, is one of the first independent wafer bumping service providers in Malaysia.<br />

At UAT we offer a one-stop center for wafer bumping services which includes gold bumps, electroplated solder bumps<br />

through “ball drop” process. We also offer pad redistribution and repassivation for wafer sizes of 4, 6 and 8-inch diameter.<br />

Unisem Europe Ltd.<br />

Bernard Ramsay<br />

European Sales Director<br />

Parkway, Pen-y-fan Industrial Estate<br />

Crumlin<br />

South Wales NP11 3XT<br />

Bernie.Ramsay@Unisem-eu.com<br />

Cell/Mobile +44 (0)7779 657696<br />

Unisem USA<br />

Mike Stokman<br />

North American VP of Sales<br />

Unisem USA<br />

1893 Klondike Road<br />

Livermore<br />

CA 94550<br />

Mike.stokman@unisem-us.com<br />

Cell/Mobile + 925 980 6515

CONTENTS<br />

The International Magazine of <strong>Chip</strong>-<strong>Scale</strong><br />

Electronics, Flip-<strong>Chip</strong> Technology, Optoelectronics<br />

Interconnection and Wafer-Level Packaging<br />

March 2007<br />

Volume 11, Number 2<br />

THE COVER<br />

Someone (was it old Will Shakespeare, again?)<br />

once said, “There’s nothing new under the sun.”<br />

We beg to differ! There’s lots new, especially in the<br />

machines that are used to package the chips we all<br />

love (and either directly or indirectly profit from).<br />

Over the past few years, we’ve seen a consolidation<br />

in the sub-industries that make wire bonders and die<br />

attach. It’s been less than two years since pioneer<br />

Kulicke & Soffa Industries sold its wedge bonding<br />

product line to Orthodyne, probably a smart move<br />

for both. And almost while we weren’t looking, The<br />

former ESEC, after becoming a Unaxis brand,<br />

became an Oerliken brand!<br />

Editor Ron Iscoff looks at the good and bad of today’s<br />

wire bonders, and Orthodyne chips in with a new<br />

ribbon bonding process. Meanwhile, Terry Thompson,<br />

our senior editor from the cold climes of the Midwest,<br />

shook off the snow long enough to report on<br />

machines for die attach and flip-chip packaging.<br />

(Illustration for <strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> by<br />

Design 2 Market) [design2marketinc.com]<br />

COVER FEATURES<br />

Are Wire Bonders Running Out of Steam? 28<br />

How this Essential IC Assembly Tool Is Keeping Pace<br />

Ron Iscoff, Editor<br />

Wire bonders are becoming smarter, faster and more cost-effective on<br />

the assembly line. In the bonder’s 50+ year history, the machines have<br />

become not only the icon for IC assembly, but the most-needed tool at<br />

every IC assembler. Is there room for improvement? Of course, and<br />

we’ll explore that topic in this article.<br />

International Directory of Production Wire Bonders<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> Staff<br />

34<br />

Flip-<strong>Chip</strong> Processing Secrets:<br />

36<br />

Saving Money and Saving Time<br />

Terrence E. Thompson, Senior Editor<br />

The biggest “secret” to successful, automated flip-chip production is<br />

the careful selection of the increasingly intelligent equipment that makes<br />

the technology more affordable, reliable and amazingly accurate. Your<br />

choice of the best tools for your applications is going to result in your<br />

company either saving lots of money, or—alternatively—writing a<br />

check for a dust-gathering behemoth that spends much of its time<br />

sitting in a corner like a wallflower at the prom.<br />

International Directory of Flip <strong>Chip</strong> & Die Attach Bonders/Aligners<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> Staff<br />

43<br />

The Challenge of Packaging Small Power Devices 45<br />

Dr. Christoph Luechinger and Siegbert Haumann,<br />

Orthodyne Electronics Corp.<br />

Until recently, fine wire ball bonding and Cu strap attachment were the<br />

main interconnect techniques for power semiconductors smaller than the<br />

TO-252. A new, large aluminum ribbon bonding process, however, has<br />

overcome past size restrictions, enabling the use of this technology to<br />

overcome weaknesses in traditional approaches.<br />

CONTINUED >><br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong>, at 7291 Coronado Dr., Suite 8, San Jose, CA 95129<br />

(ISSN 1526-1344), is published eight times a year, with issues in<br />

January-February, March, April, May-June, July, August-September,<br />

October and November-December.<br />

Periodical postage paid at San Jose, Calif., and additional offices.<br />

POSTMASTER: Send address changes to <strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> magazine,<br />

7291 Coronado Dr., Suite 8, San Jose, CA 95129.<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ March 2007 ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 1

CONTENTS<br />

FEATURE ARTICLE<br />

High-Speed Stencil Cleaning Techniques for IC 53<br />

Substrate-Level Assembly Lower Total Costs<br />

Trevor Warren, DEK<br />

Printing-type processes have quickly earned acceptance<br />

in semiconductor and other sophisticated packaging<br />

applications. Stencil printing is an enabling technology<br />

for many wafer-bumping and similar uses. Integrating<br />

proven, innovative stencil cleaning process improvements<br />

into operations, for example, is a very efficient<br />

way for companies to control costs and improve yields.<br />

LATE NEWS<br />

STATS <strong>Chip</strong>PAC Joins Billion-Dollar-Buyout Club<br />

Singapore—Less than four months after the Carlyle Group bid $5.4 billion<br />

for Advanced Semiconductor Engineering, Taiwan, a Singapore group has<br />

offered to buy out STATS <strong>Chip</strong>PAC’s available unowned shares for cash.<br />

In late February, Temasek Holdings Pte., Singapore’s state-owned investment<br />

company, offered up to $1.6 billion for all remaining shares of the Singaporebased<br />

IC assembly and test provider. Temasek’s wholly-owed subsidiary<br />

Singapore Technologies Semiconductors Pte. currently owns 35.6 percent of<br />

STATS <strong>Chip</strong>PAC. [statschippac.com]<br />

DEPARTMENTS<br />

Publisher’s Letter Gene Selven<br />

We’re counting our ABCs for you!<br />

Assembly Lines Ron Iscoff<br />

Farewell to two remarkable leaders<br />

Standards Mark Bird<br />

Package-on-Package is ready to take-off<br />

Test Patterns Paul M. Sakamoto<br />

The ‘mainframe mentality’ lives on!<br />

Industry News<br />

Calendar<br />

WLCSP Forum Manuel H. Mere<br />

Ongoing migration to finer WLCSP pitches<br />

Inside Patents A. Jason Mirabito and Carol Peters<br />

Underfill: patent offers a new approach to an old problem<br />

Index to 2006 Articles<br />

What’s New!<br />

Back of the Book Dr. David Tuckerman<br />

5 critical challenges for 3D packaging<br />

Ad Index/More News/Sales Offices<br />

5<br />

7<br />

8<br />

10<br />

13<br />

21<br />

52<br />

57<br />

58<br />

60<br />

62<br />

64<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ March 2007 ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 3

Technologies, Inc.<br />

Your Global Provider of Leading Edge<br />

Semiconductor Packages<br />

NTK Technologies<br />

offers a wide range<br />

of cutting-edge<br />

ceramic and organic<br />

packages for<br />

ASIC<br />

MPU<br />

Sensors<br />

MEMS<br />

• computer<br />

• consumer<br />

• telecom<br />

• medical<br />

• automotive<br />

• and hi rel<br />

products<br />

Multi-Layer<br />

High Frequency<br />

OPTO<br />

RF<br />

High Reliability<br />

High Density<br />

Visit us at OFC<br />

Booth #1003 March 27-29<br />

Anaheim Convention Center<br />

Phoenix, Irvine, San Jose, Chicago, Boston, Austin, Dallas,<br />

Arizona California California Illinois Massachusetts Texas Texas<br />

602/470-9898 949/580-0607 408/727-5180 847/788-9795 508/820-0220 512/340-0194 972-235-1625<br />

Visit our web-site at www.ntktech.com

VOLUME 11, NUMBER 2<br />

The International Magazine of <strong>Chip</strong>-<strong>Scale</strong><br />

Electronics, Flip-<strong>Chip</strong> Technology, Optoelectronic<br />

Interconnection and Wafer-Level Packaging<br />

STAFF<br />

Gene Selven Publisher<br />

7291 Coronado Dr., Ste. 8, San Jose, CA 95129<br />

b 408.996.7016 > 408.996.7871<br />

gselven@aol.com<br />

Ron Iscoff Editor & Associate Publisher<br />

929 Ebbetts Ave., Manteca, CA 95337<br />

b 209.824.1289 > 209.644.7747<br />

chipscale@gmail.com<br />

Terrence Thompson Senior Editor<br />

2303 Randall Rd. #140, Carpentersville, IL 60110<br />

b 847.515.1255<br />

tethompson@aol.com<br />

Steve Berry Contributing Editor<br />

b 408.369.7000 > 408.369.8021<br />

saberry@electronictrendpubs.com<br />

Dr. Tom Di Stefano Contributing Editor<br />

b 408.399.4501 > 408.395.0448<br />

tom@centipedesystems.com<br />

Dr. Subash Khadpe Contributing Editor<br />

skhadpe@semitech.com<br />

Harvey S. Miller Contributing Editor-at-Large<br />

b 650.328.4550 > 650.327.2360<br />

h.miller@ieee.org<br />

Paul M. Sakamoto Contributing Editor–Test<br />

b 925.924.9110 x148<br />

paul.sakamoto@inovys.com<br />

Sandra Winkler Contributing Editor<br />

b 408.369.7000 > 408.369.8021<br />

slwinkler@electronictrendpubs.com<br />

The Official Publication of the WLCSP Forum<br />

SUBSCRIPTION INQUIRIES<br />

Judy Levin <strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong><br />

7291 Coronado Dr., Ste. 8, San Jose, CA 95129<br />

b 408.996.7016 > 408.996.7871<br />

csrsubs@chipscalereview.com<br />

ADVERTISING PRODUCTION<br />

INQUIRIES<br />

Kim Newman<br />

7291 Coronado Dr., Ste. 8, San Jose, CA 95129<br />

b 408.996.7016 > 408.996.7871<br />

csradv@aol.com<br />

REPRINTS<br />

Kim Newman b 408.996.7016<br />

8 csradv@aol.com<br />

ADVISORS<br />

Mark DiOrio MTBSolutions<br />

Dr. Tom Di Stefano Centipede Systems<br />

Charles R. Harper Technology Seminars Inc.<br />

Mark Murdza Antares Advanced Test Technologies<br />

Dr. Guna Selvaduray San Jose State University<br />

Dr. Thorsten Teutsch Pac Tech<br />

Dr. Dietrich Tönnies SUSS MicroTec AG<br />

Dr. David Tuckerman Tessera Technologies<br />

Professor C.P. Wong Georgia Tech<br />

Copyright © 2007 by Gene Selven & Associates Inc.<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> (ISSN 1526-1344) is a registered trademark<br />

of Gene Selven & Associates Inc. Publishing headquarters are<br />

located at 7291 Coronado Drive, Suite 8, San Jose, CA 95129.<br />

All rights reserved.<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> is published eight times a year.<br />

Subscriptions in the U.S. are available without charge to<br />

qualified individuals in the electronics <strong>industry</strong>. Subscriptions<br />

outside the U.S. (eight issues) by airmail are $60 per year to<br />

Canada or $60 to other countries. In the U.S., subscriptions<br />

by first class mail are $40 per year.<br />

PUBLISHER’S LETTER<br />

We’re Counting Our ABCs for You!<br />

By Gene Selven, Publisher [gselven@aol.com]<br />

As part of our continuing commitment to our advertisers and to our readers,<br />

we recently signed an agreement with the Audit Bureau of Circulations to<br />

audit the distribution of <strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong>.<br />

Our advertisers and their agencies use ABC reports and analyses as the basis for<br />

media buying decisions. Publishers use ABC-audited data to manage circulation and<br />

develop marketing strategies.<br />

We have been audited by another auditing agency for the past five years, and we did<br />

not make this change lightly. We believe, however, that ABC will provide our advertisers<br />

with a more complete and more accurate picture of our readers and subscribers.<br />

This is important to our advertisers, of course, because their sponsorship enables us<br />

to produce and mail the publication to our domestic readership gratis.<br />

We are, unlike our chief competitor, a completely independent publisher. Our business<br />

consists solely of <strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> in English and Chinese; a web <strong>news</strong>letter and our<br />

International Wafer-Level Packaging Conference, which is jointly presented with the SMTA.<br />

We are also the leading publication in terms of both advertising revenue and editorial<br />

pages. We have worked hard to achieve this position—one which we’ve held for the last<br />

four years—and we aim to stay on top!<br />

Everyone will have total access to our semi-annual circulation audits. They will be<br />

posted on our web site at www.chipscalereview.com, and we invite you to visit anytime<br />

to see for yourself. Our first ABC audit will be available in June.<br />

By the way, I want to assure you that we will continue to guard your privacy. When<br />

the audit information is gathered, individual subscriber names are never released nor<br />

sold to any company without an individual’s prior explicit permission.<br />

China Bound<br />

As the March issue goes to press, I am preparing for my fourth annual trip to SEMICON<br />

China in Shanghai.<br />

To serve the booming China market, we publish two issues in Chinese each year. The<br />

first is for SEMICON China in March; the second is distributed at NEPCON South China,<br />

Shenzhen, in August. This year we will distribute nearly 10,000 copies in Shanghai.<br />

Over the past four-plus years, I’ve witnessed China’s amazing growth personally and<br />

have spoken to many of the individuals and companies responsible for it.<br />

We’re now in the early stages of preparing our NEPCON South China issue for distribution<br />

in Shenzhen.<br />

Please contact me or one of our representatives about placing your ad in this issue.<br />

If you’re planning to sell in China, you must make your name, company and products<br />

known—preferably in the Mainland’s own language. i<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ March 2007 ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 5

ASSEMBLY LINES<br />

Farewell to Two Remarkable Leaders<br />

By Ron Iscoff, Editor [chipscale@gmail.com]<br />

The man who pioneered the disk<br />

drive and went on to create an<br />

<strong>industry</strong> has died.<br />

The man who built the world’s largest<br />

supplier of semiconductor assembly and<br />

packaging equipment has retired.<br />

Alan F. “Al” Shugart, author, entrepreneur,<br />

engineer, salesman, aficionado of<br />

eye-catching Hawaiian shirts, and<br />

founder of disk-drive makers Shugart<br />

Associates and Seagate Technology, died<br />

in December at age 76 in Monterey, Calif.<br />

His death was the result of complications<br />

from heart surgery, according to<br />

the New York Times.<br />

Over the past three decades, I met<br />

with Al about a dozen times in my role<br />

as a trade journalist.<br />

The last time I saw him was more<br />

than a decade ago at a San Jose conference,<br />

DISKON, an event for disk drive<br />

<strong>industry</strong> people.<br />

He was the keynoter, and while I<br />

don’t recall the subject of his talk, it was<br />

controversial and spiced with his<br />

unique wit. He mentioned in his talk,<br />

that he didn’t care very much for<br />

lawyers. He also said that excluded his<br />

daughter, Teri, who is a lawyer.<br />

Al was a native of Chino, Calif., and he<br />

studied engineering at the University of<br />

the Redlands, where he earned a bachelor’s<br />

degree in engineering physics. The<br />

day after he graduated, he went to work<br />

for IBM as a field service engineer.<br />

In 1955, while at the IBM Research<br />

Labs in San Jose, he led the team that<br />

developed the first hard disk drive,<br />

RAMAC (Random Access Method<br />

of Accounting and Control).<br />

He was also a political curmudgeon,<br />

who often had little<br />

patience with the dirty deeds of<br />

most politicos. In 1996, he<br />

attempted to place his dog,<br />

Ernest, on the ballot for congressman.<br />

He recounts this episode in<br />

his book, Ernest Goes to<br />

Washington.<br />

He’s also the author of<br />

Fandango: The Story of Two Guys<br />

Who Wanted to own a Restaurant,<br />

(which Al did), and The Wit and<br />

Wisdom of Al Shugart.<br />

In 1998, he left Seagate, which<br />

he had formed into the world’s<br />

largest independent maker of disk<br />

drives, to found Al Shugart<br />

International, a resource center to<br />

help budding entrepreneurs transform<br />

“great ideas into great companies with<br />

lasting value,” according to his web site<br />

[alshugart.com].<br />

The Story of ASM<br />

I have kept the Wiley-Asia book,<br />

Soaring Like Eagles in a coveted spot in<br />

my bookcase for about a year, since I<br />

received a review copy. Now that spring<br />

cleaning is here, the book has surfaced<br />

again and begs for comment.<br />

The authors are Patrick Lam, founder of<br />

ASM Pacific Technology, and Dr. Edmund<br />

Lam, who is Patrick’s son and a professor<br />

of electrical and electronic engineering<br />

at the University of Hong Kong.<br />

Al Shugart, the king of Hawaiian shirts. (Courtesy Chris Shugart)<br />

Although I suspect its publication<br />

was subsidized by the elder Lam, it’s a<br />

book worthy of discussion. As the book<br />

points out, ASM has maintained profitable<br />

growth for more than 30 years.<br />

Not everyone can say that!<br />

The book is subtitled, “ASM’s High-<br />

Tech Journey in Asia,” and within its<br />

modestly sized 250 pages, the Lams<br />

detail their journey from 1975—the<br />

founding—through 2005, when the<br />

book was printed.<br />

If you’re aligned with the equipment<br />

<strong>industry</strong>—semiconductor or otherwise—<br />

it’s likely you will learn a thing or two<br />

in this slender tome’s pages.<br />

Continued on page 63 >><br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ March 2007 ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 7

STANDARDS<br />

Package-on-Package Is Ready to Take-off<br />

By Mark Bird, Contributing Editor<br />

The Package-on-Package (PoP)<br />

family is one of the fastest<br />

growing formats in the market.<br />

In 2005, PoPs accounted for unit volumes<br />

of 100 million. Last year, that<br />

unit volume nearly doubled to 180+<br />

million and is expected to soar to<br />

around 700 million by 2010.<br />

The need for the PoP is to provide a<br />

cost-effective format for logic and<br />

memory stacking in the <strong>industry</strong> to<br />

address technical, business and logistic<br />

requirements.<br />

Dynamic Growth<br />

The <strong>industry</strong> has witnessed a range of<br />

new development programs and a mixture<br />

of non-standard solutions for PoPs<br />

over the past few years. The adoption of<br />

PoPs in 2004 greatly advanced mobile<br />

phone applications. In addition, the<br />

development of the JEDEC <strong>industry</strong><br />

standards have stimulated rapid PoP<br />

growth in volume, growth in applications<br />

and in the infrastructure. This<br />

dynamic growth has been experienced<br />

since early 2005.<br />

The PoP market is ready for take-off.<br />

JEDEC JC-63, the Stacked Package<br />

Product Committee has standardized<br />

the pinouts and functionality. The package<br />

registration outlines for the bottom<br />

and top packages have been addressed<br />

by the JC-11 Packaging Committee.<br />

A design-guide standard has also<br />

been created to address future configurations.<br />

This standardization coordination<br />

between the JEDEC committees<br />

allows the end-customer the flexibility<br />

to buy the lower, upper and stacked<br />

combination from a variety of different<br />

suppliers, giving the end-customer the<br />

ability to take advantage of high volumes<br />

at the lowest possible assembly and<br />

packaging costs.<br />

The three JC-11 outline registrations<br />

and design guide are:<br />

• Lower PoP Package; Very Thin Profile;<br />

Fine Pitch; Square;<br />

• Stackable Ball Grid 0.50mm Ball Pitch<br />

Array Family-MO-266<br />

• Upper PoP Package; Low Profile, Thin<br />

Profile and Very Thin Profile; Fine<br />

Pitch; Square; 0.65 and 0.50mm Ball<br />

Pitch Array Family-MO-273.<br />

Future Configurations<br />

The Lower and Upper PoP Design Guide<br />

was established to set the stage for<br />

future configurations. The Design<br />

Guide is 4.22, Issue A and was published<br />

in November 2005.<br />

PoP with single bottom die<br />

PoP with stacked bottom die<br />

The latest package registration<br />

revision is available at www.jedec.org<br />

in PDF format for downloading at<br />

no charge.<br />

All three PoP standards will undergo<br />

revisions to add 0.80mm ball pitch for<br />

the upper packages, as well as 0.40mm<br />

ball pitch for the lower package. This<br />

The <strong>industry</strong> has witnessed a range of new development programs and<br />

a mixture of non-standard solutions for PoPs over the past few years.<br />

would mean additional variations to the<br />

registration outlines, as well as an update<br />

to the Lower and Upper PoP Design<br />

Guide. The projected time of this activity<br />

will be late this year. i<br />

Mr. Bird is a Technology Fellow and the<br />

COO at Mbird and Associates Semiconductor<br />

Assembly, Packaging and Standardization<br />

Consultants in Apache Junction, Ariz. He<br />

is also the chairman of the JC-11 Packaging<br />

Standards Committee and technical<br />

advisor/chief delegate for the United States<br />

to the IEC TC47 and SC47D Semiconductor<br />

Committees. [j_mark_bird@yahoo.com]<br />

8<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ March 2007 ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

plasma cleaning solutions<br />

With productivity 150% of conventional<br />

models and patented parallel plate<br />

technology that delivers superior<br />

results for both etching and<br />

surface modification, interest in<br />

Panasonic’s plasma solution<br />

continues to skyrocket.<br />

Experience <strong>industry</strong>-leading<br />

mold resin adhesion and under-fill<br />

wettability, reduced incidence<br />

peel-off, voids and cracks.<br />

Ideal for all manufacturers<br />

and for all volume levels.<br />

It’s brilliant.<br />

PSX303

TEST PATTERNS<br />

The ‘Mainframe Mentality’ Lives On!<br />

By Paul M. Sakamoto, Contributing Editor–Test [paul.sakamoto@inovys.com]<br />

I<br />

would guess that about half of<br />

you who read this column<br />

remember the time when mainframe<br />

computers roamed the land.<br />

The closely related mini-computer<br />

was its scaled-down little brother. Aside<br />

from the fact that they were very large<br />

by today’s standards, these machines all<br />

had proprietary operating systems and<br />

programming languages.<br />

This required specialized training for<br />

the various models from different manufacturers.<br />

Additionally, the networking<br />

between these machines was very difficult<br />

and aided the growth of specialized<br />

companies to address the task.<br />

Slow to Adopt Standards<br />

The biggest reason that the <strong>industry</strong> was<br />

slow to adopt standards was that it<br />

allowed vendors to keep their customers<br />

virtually enslaved once users adopted a<br />

maker’s proprietary system.<br />

It also allowed the manufacturer to<br />

charge for a very wide variety of related<br />

goods and services that only they could<br />

provide.<br />

Fortunately, today we have standards<br />

for software, applications and networking<br />

that are applied very broadly. These<br />

standards allow the direct re-use of data<br />

and information on virtually all current<br />

computers, smart phones, PDAs, and<br />

other computing machines.<br />

My rant today is that this is not the<br />

case for ATE.<br />

3600Plus & 3700Plus<br />

More performance with<br />

fewer limitations.<br />

The 3600Plus and 3700Plus wire bonders break new ground<br />

in innovation and design. Offering you more performance,<br />

options and versatility, the Plus Series combines intuitive<br />

technology with quality and reliability:<br />

• PowerRibbon TM Option for ribbon sizes 20 mil x 4 mil to<br />

80 mil x 8 mil<br />

• Bond Process Monitoring (BPM) flags suspect bonds in<br />

real-time, stores process information for later evaluation<br />

• Active Loop Control (ALC) bondheads allow best-in-class<br />

loop control and non-destructive pulltesting<br />

• Offline Programming Tool (OPT) converts CAD files into<br />

machine process programs, maximizing machine uptime<br />

New machine capabilities for greater performance, new<br />

international offices for better service, and a new interconnect technology<br />

— Orthodyne is committed to giving customers more.<br />

10<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ March 2007 ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

Now, some of you may say, “Hey,<br />

Paul, you’re wrong. Company ABC<br />

adheres to the IEEE x standard.”<br />

This is likely true, but it is completely<br />

not the point. One could also say,<br />

“What about the Semiconductor Test<br />

Consortium/Open Architecture<br />

Initiative?” It’s a decent shot, but so<br />

far is more widely talked about than<br />

widely used. What I am talking about is<br />

the ability to develop a program on a<br />

tester from one company and run it on<br />

a standards-compliant tester from<br />

another company without any new<br />

programming.<br />

This just doesn’t happen today. The<br />

programming languages for each tester<br />

are different enough to require a conversion<br />

process for all program porting.<br />

This is a time-consuming and expensive<br />

process in most cases. It can also be<br />

error-prone, which is the most expensive<br />

problem of all.<br />

Mainframe Mentality<br />

The main reason that ATE companies<br />

promulgate the proprietary model—<br />

while sending delegates to standards<br />

meetings—is that they still have the old<br />

mainframe mentality.<br />

These manufacturers hope to protect<br />

their domains by making sure their customers<br />

are enslaved by their sunk cost<br />

in training, programs, infrastructure<br />

and other legacy ballast. The customers<br />

become enslaved by their own expertise<br />

with these systems.<br />

The cost of this model is high to all<br />

parties. The ATE companies miss the<br />

leverage of having the common issues<br />

be common. That is, they spend a lot of<br />

time working out the details of their<br />

Mainframe computers have come along way over<br />

the years. This is a photo of the original ENIAC<br />

computer that occupied a football-sized room.<br />

(U.S. Army photo)<br />

proprietary language and architecture<br />

instead of spending those resources on<br />

market differentiation and added value.<br />

Continued on page 63 >><br />

Patent Pending<br />

PowerRibbon <br />

More power with<br />

fewer connections.<br />

For years, Orthodyne’s ultrasonic small and large wire bonders have led the<br />

market in innovation and efficient, reliable performance. Our new<br />

PowerRibbon technology extends that tradition as it creates a new<br />

category of interconnect for power devices.<br />

Sized 20 x 4 mil to 80 x8mil,PowerRibbonoffers the solution to smaller<br />

packaging – more power with fewer connections. PowerRibbon combines<br />

the flexibility and robustness of large aluminum wire bonding<br />

with greater current-carrying capacity and lower RDS ON . Efficient, reliable<br />

and retrofittable, PowerRibbon is the most advanced interconnect<br />

alternative for small SO8, PQFN type leadframe applications as well<br />

as complex power modules.<br />

To find out more about PowerRibbon or the Plus Series<br />

bonders, contact us.<br />

16700 Red Hill Avenue<br />

Irvine, CA 92606-4802<br />

Phone: +1-949-660-0440<br />

sales@orthodyne.com<br />

www.orthodyne.com<br />

Orthodyne Electronics GmbH<br />

Lina-Ammon-Strasse 15<br />

90471 Nuernberg, Germany<br />

Ph: +49-(0)911-98813-0<br />

Fax: +49-(0)911-98813-20<br />

Laerchenster. 2<br />

83533 Edling, Germany<br />

Ph: +49-8071-93215<br />

Fax: +49-8071-93217<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ March 2007 ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 11

More than meets the eye<br />

Compatibility-proven Material Sets from Henkel.<br />

Trust Henkel's Material Sets that truly work together.<br />

Trying to force non-optimized materials to work together in advanced packages and<br />

assemblies? At Henkel, our materials are specifically designed to work together, delivering<br />

tested, reliable and guaranteed compatible material sets for all of your semiconductor<br />

packaging and circuit board assembly requirements.<br />

Contact our application experts today for material set solutions that work:<br />

Henkel Americas: +1 949 789 2500 Henkel Europe: +44 1442 278 000 Henkel Asia: +852 2233 0000<br />

Across the Board. Across the Globe.<br />

Loctite, Hysol and Multicore are trademarks of Henkel Corporation, U.S.A. © Henkel Corporation, 2007. All rights reserved. 4178 01/2007<br />

www.electronics.henkel.com

INDUSTRY NEWS<br />

APEX 2007 Los Angeles: A Report from Smogville<br />

By Ron Iscoff, Editor<br />

The IPC’s APEX show,<br />

which trimmed the sails<br />

from the venerable<br />

and—until 2000—<br />

unchallenged NEPCON<br />

West behemoth seven<br />

years ago, has transformed<br />

itself into a<br />

regional printed circuit<br />

board show.<br />

This is not surprising,<br />

since it’s co-located with<br />

the same trade group’s<br />

Printed Circuits Expo.<br />

Regional Show<br />

Certainly, there is nothing wrong<br />

with a regional printed circuits<br />

show, but there’s also not much to<br />

Teraflop Computer Shrinks to Fingernail-Sized Processor<br />

Santa Clara, Calif.—Intel<br />

Corporation researchers<br />

have developed the world’s<br />

first programmable processor<br />

that delivers supercomputer-like<br />

performance from<br />

a single 80-core chip not<br />

much larger than the size of<br />

a fingernail. The processor<br />

uses less electricity than most<br />

of today’s home appliances—<br />

just 62 watts.<br />

The “Tera-scale computing”<br />

research is aimed at delivering<br />

teraflop—or trillions of calculations<br />

per second—performance.<br />

Technical details of the teraflop<br />

research chip were presented in<br />

February at the annual International<br />

Solid State Circuits Conference in<br />

San Francisco.<br />

The teraflop chip also features a<br />

mesh-like “network-on-a-chip”<br />

It’s 50 years for IPC and the fourth location for APEX this<br />

year. Visitors benefitted from generally excellent weather and<br />

a revitalized downtown Los Angeles. (<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong>)<br />

see for chip devotees, unless they’re<br />

also making printed circuit boards.<br />

And there’s no reason, really, to<br />

Continued on page 15 >><br />

This board houses Intel’s 80-core teraflops research<br />

chip. The board contains working silicon and is the<br />

world’s first programmable chip to achieve teraflops<br />

performance while consuming very little power. (Intel)<br />

architecture that enables super-high<br />

bandwidth communications<br />

between the cores, and is capable of<br />

moving terabits of data per second<br />

inside the chip.<br />

Intel has no plans to bring this<br />

exact chip designed with floating<br />

point cores to market.<br />

Continued on page 15 >><br />

IBM and Intel Claiming<br />

45nm Transistor Honors<br />

Intel President Paul Ottolini holds an Intel Core 2 Duo<br />

microprocessor. (Intel Corp.)<br />

San Jose—In announcements released<br />

nearly simultaneously, giants IBM and<br />

Intel are both claiming next-generation 45<br />

nanometer transistor honors employing<br />

separate processes with apparently similar<br />

materials.<br />

Intel, Santa Clara, calls its technology,<br />

“The biggest change to computer chips in<br />

40 years” and “one of the biggest advancements<br />

in fundamental transistor design.”<br />

IBM, Yorktown Height, N.Y., terms its work<br />

“The first fundamental change to the basic<br />

transistor in 40 years.” Neither company<br />

names the other in their <strong>news</strong> releases.<br />

Continued on page 19 >><br />

A New Interconnection Technology<br />

Blooms at Jerry Falwell’s University<br />

Los Angeles—What do the Rev. Jerry<br />

Falwell and Liberty University, the fundamentalist<br />

Baptist institution he founded,<br />

have in common with the semiconductor<br />

<strong>industry</strong>?<br />

Until recently, the answer would have<br />

been nothing.<br />

Continued on page 24 >><br />

INSIDE NEWS<br />

• Worldwide Silicon Shipments Rise by 20<br />

Percent page 64<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ March 2007 ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 13

14<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ March 2007 ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

INDUSTRY NEWS<br />

APEX Continued from page 13 >><br />

exhibit unless you’re selling to the folks<br />

who make, sell or buy PWBs.<br />

As I made my rounds, the comments<br />

were mixed, but generally favorable<br />

about the show. Most of the people I<br />

spoke to thought the show was much<br />

smaller this year.<br />

Not so! said Anna Garrido, the IPC’s<br />

marketing and communications lady,<br />

when I questioned her in the press room.<br />

During the three-day run of exhibits,<br />

floor traffic was modest on Tuesday and<br />

Wednesday and slowed to a trickle on<br />

the third and final day. It would not be a<br />

challenge for most people to cover all<br />

exhibits in one day.<br />

According to a 2006 IPC <strong>news</strong> release,<br />

some 14,967 square meters (161,000 square<br />

feet) of the Convention Center were expected<br />

to be occupied by exhibitors. Attendance<br />

figures were not were not forthcoming by<br />

our deadline, two weeks after the show.<br />

In fact, she reported, this year’s APEX<br />

boasted more exhibitors and more overall<br />

exhibit space than the prior year. It<br />

didn’t seem like it to me or almost<br />

everyone else I talked to. Perhaps it was<br />

the lack of skyscraper exhibits which<br />

Booth arrangements presented a clear “line-ofsight”<br />

from one end of the hall to the other.<br />

we’ve come to expect, with their cantilevered<br />

rooftops and meeting rooms<br />

on second or third levels.<br />

Could the problem be the location—<br />

The Los Angeles Convention Center that<br />

dominates two massive city blocks in<br />

downtown Smogville.<br />

Fourth Location<br />

This was the fourth location for APEX<br />

since its first show in 2000. The Printed<br />

Circuits Expo, which was initially a separate<br />

event, was joined at the shoulder<br />

to APEX in 2004. In 2000, NEPCON<br />

West ran a bifurcated show in Anaheim,<br />

about two weeks before APEX. And then<br />

NEPCON West ran out of steam as the<br />

IPC cut NEPCON’s excessive exhibiting<br />

prices by half.<br />

Continued on page 26 >><br />

Intel Continued from page 13 >><br />

However, the research is instrumental in<br />

investigating new innovations in individual<br />

or specialized processor or core<br />

functions, the types of chip-to-chip and<br />

chip-to-computer interconnects required,<br />

and—most importantly—how software<br />

will need to be designed to leverage<br />

multiple processor cores most efficiently.<br />

Power Cores On/Off<br />

The research also investigated methods<br />

to power cores on and off independently,<br />

so only the ones needed to complete a<br />

task are used, providing more energy<br />

efficiency.<br />

Further research will focus on the<br />

addition of 3-D stacked memory to the<br />

chip. The Tera-scale program has over<br />

100 projects.<br />

ASCI Red, the first computer to benchmark at a<br />

Teraflops in 1996, used nearly 10,000 Pentium<br />

Pro CPUs.<br />

Teraflop performance was first<br />

achieved in 1996, on the ASCI Red<br />

Supercomputer built by Intel for Sandia<br />

National Laboratory.<br />

That computer occupied more than<br />

186 square meters, was powered by nearly<br />

10,000 Pentium Pro processors, and<br />

consumed over 500kW. [intel.com] ■<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ March 2007 ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 15

INDUSTRY NEWS<br />

APEX 2007 PHOTO ALBUM<br />

The APEX conference, co-located with IPC’s<br />

Tuesday – Thursday FEBR<br />

Printed Circuits Expo and Designers Summit,<br />

Los Angeles Convention Cente ®<br />

enjoyed mostly sunny skies for its first year in Los<br />

®<br />

FOR MORE INFORMATION Angeles. Next year, the event is scheduled to return<br />

and the DESIGNERS SUMMIT<br />

contact 877-472-4724 (US/Can to the Los Angeles Convention Center from<br />

February 17-21, with exhibits running from February 19-21. (See the editor's<br />

report beginning on page 13.)<br />

Show visitors included Jerry Cohen, president of<br />

Pure Technologies, Atlanta, and his First Lady,<br />

Marsha Cohen.<br />

Dage, a maker of bond testers and x-ray inspection<br />

equipment, had a new owner, Nordson, at this<br />

year’s APEX.<br />

Finetech’s Adrienne Gerard and Neil O’Brien discussed<br />

direct component printing with show visitors.<br />

Gene Selven, <strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> publisher,<br />

stopped to chat with Heraeus’ Christina Kistler.<br />

16<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ March 2007 ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

INDUSTRY NEWS<br />

As usual, Panasonic’s exhibit was a dazzler—big, bold and brassy!<br />

Henkel’s Doug Dixon and Elaine Yee talk<br />

about the company’s new products.<br />

George Tint of HDI Solutions, Santa Clara, demonstrates<br />

the HIOKI Hi-Tester.<br />

Ron Levinson (left), <strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> representative,<br />

stops by to chat with Alec Moffat of Machine<br />

Vision Products.<br />

Don Miller, president of YESTech, San Clemente,<br />

Calif., demonstrates a new product.<br />

Paul Niemczura, Heraeus’ manager of<br />

technology development, makes a point.<br />

The Indium booth once again gets our vote for the most<br />

esthetically pleasing exhibit at APEX.<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ March 2007 ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 17

Solve Your Lead-Free Puzzle with Kester<br />

Kester’s set of compatible lead-free materials makes lead-free<br />

assembly a snap. Whether it’s for SMT, Wave Soldering, Hand<br />

Soldering or Rework applications, Kester has reliable Lead-Free<br />

Solutions specifically tailored for your assembly needs.<br />

EnviroMark907 No-Clean Solder Paste<br />

• Excellent wetting and shininess<br />

• Extremely print friendly<br />

• #1 globally specified lead-free paste<br />

Visit Us at<br />

APEX<br />

Booth #1542<br />

K100LD Bar Solder<br />

• Lowest copper dissolution<br />

• Silver-free and low-dross to lower costs<br />

• Shiny joints with excellent process yields<br />

959T Alcohol-Based and 979 VOC-Free Fluxes<br />

• Excellent hole-fill<br />

• Low voids<br />

• High reliability no-clean with low residues<br />

Global Headquarters<br />

800 W. Thorndale Avenue<br />

Itasca, IL 60143<br />

Phone: 800 2.KESTER<br />

(+1) 847.297.1600<br />

Fax: (+1) 847.390.9338<br />

website: www.kester.com<br />

Branches: Canada • Mexico • Brazil • Germany • Japan •<br />

Singapore • Taiwan • Malaysia • China<br />

275 No-Clean Cored Wire<br />

• Fast wetting for efficient soldering<br />

• Minimal smoke and low odor<br />

• Available in K100LD and SAC305 alloys<br />

Call Kester today for your complete<br />

Global Lead-Free Solutions package.

INDUSTRY NEWS<br />

IBM and Intel Continued from page 13 >><br />

High-k + Metal Gate Transistors<br />

Metal Gate<br />

• Increases the gate field effect<br />

High-k Dielectric<br />

• Increases the gate field effect<br />

• Allows use of thicker dielectric<br />

layer to reduce gate leakage<br />

HK + MG Combined<br />

• Drive current increased >20%<br />

(>20% higher performance)<br />

• Or source-drain leakage<br />

reduced >5x<br />

• Gate oxide leakage reduced >10x<br />

S<br />

HK+MG<br />

Transistor<br />

Silicon Substrate<br />

Low resistance layer<br />

Metal gate<br />

Different for NMOS and PMOS<br />

High-k gate oxide<br />

Hafnium based<br />

D<br />

combined: The problems are Fermilevel<br />

pinning and “phonon scattering.”<br />

Joint Development<br />

IBM’s work has been conducted jointly<br />

with Sony, Toshiba and Intel’s arch<br />

nemisis AMD.<br />

IBM says it has already “inserted” the<br />

technology into its East Fishkill, N.Y.,<br />

fab and will begin to produce ICs at<br />

45nm beginning next year.<br />

This technology, termed “high-k<br />

metal gate,” substitutes a material in<br />

place of Si, although the material type<br />

was not disclosed. [ibm.com]<br />

[intel.com] ■<br />

This graphic, based on Intel-supplied information,<br />

illustrates the company’s 45nm High-k + metal<br />

gate transistor.<br />

Next-Generation CPUs<br />

Intel says the process will be employed<br />

in its next-generation of Core 2 CPUs—<br />

already in house—the first of at least 15<br />

45nm processor products in development<br />

at the company.<br />

The development, Intel adds, will<br />

enable “record speeds,” while reducing<br />

electrical leakage that can adversely<br />

affect power consumption, noise and<br />

costs.<br />

It will also ensure that Moore’s Law<br />

“will thrive well into the next decade,”<br />

the microprocessor leader claims.<br />

Intel says it is using a new material<br />

combination of high-k gate dielectrics<br />

and metal gates. The company will begin<br />

production of the first 45nm CPU<br />

(Penryn) in the second half of this year.<br />

Intel Beating the Competition<br />

Its development is more than a year<br />

ahead of its competitors, Intel claims.<br />

In its 45nm technology, Intel has<br />

employed a hafnium-based, high-k<br />

material in the gate dielectric. The<br />

dielectric is created with atomic layer<br />

deposition (ALD), where a single layer<br />

of the high-k material molecule is<br />

deposited at a time.<br />

Because the high-k gate dielectric is<br />

not compatible with current Si gate<br />

electrodes, Intel said it had to develop<br />

the new metal gate materials to solve two<br />

problems that arise when the two are<br />

CORWIL is the leader in wafer backgrinding, wafer dicing and visual<br />

inspection to commercial, military and medical specs. CORWIL’s newest<br />

addition in dicing equipment is a fully automatic, latest state-of-the-art<br />

12 inch dicing saw that strengthens CORWIL’s technical leadership for<br />

chip-free and fast turn-around dicing. CORWIL dices Si, GaAs, Sapphire,<br />

SiGe, laminates and many other materials and CORWIL is unsurpassed<br />

in IC assembly in ceramic, BGA, flip-chip, and MLF/QFN type packages.<br />

➢ High Volume — Millions of dice per month<br />

➢ Automatic High-Speed Pick-and-Place<br />

➢ Automatic Vision Inspection Systems<br />

➢ Low K, MEMS and Optical/Imaging wafers processed<br />

➢ Experts in Multi-die Type Wafer dicing<br />

➢ Highest Quality and Best Service in the Industry<br />

Since 1990 CORWIL has built its reputation providing customers with:<br />

Excellent Quality and Superior Service<br />

Contact Us At:<br />

CORWIL Technology Corporation<br />

1635 McCarthy Blvd.<br />

Milpitas, CA 95035 info@corwil.com<br />

Tel: 408-321-6404 www.corwil.com<br />

Fax: 408-321-6407 ISO 9001:2000 Registered<br />

DSCC QML Certification<br />

MIL-PRF-38535<br />

MIL-STD-883<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ March 2007 ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 19

INDUSTRY NEWS<br />

Taiwan Will Be the Largest<br />

Equipment Market in 2007<br />

Washington, D.C.—Taiwan will be the<br />

biggest spender for chip-making equipment<br />

in 2007, according to a report<br />

published by the U.S.-Taiwan Business<br />

Council.<br />

Semiconductor Report–Annual <strong>Review</strong><br />

2006 says that 2006 was an exceptionally<br />

strong growth year for Taiwan’s leading<br />

foundry and DRAM chipmakers, and<br />

with expanded production capabilities<br />

in 300mm wafer fabs and the establishment<br />

of new partnerships, Taiwan is<br />

poised for a record year. [us-taiwan.org]<br />

Taiwan is poised for a record year.<br />

CALENDAR<br />

APRIL<br />

10-12 IPC/JEDEC Global Conference<br />

on Lead-Free Reliability and<br />

Reliability Testing for RoHS Lead-<br />

Free Electronics, Boston, Mass.<br />

[ipc.org]<br />

24-26 SMT/Hybrid/Packaging 2007,<br />

Nuremberg, Germany<br />

[smt-exhibition.com]<br />

MAY<br />

8-10 SEMICON Singapore,<br />

Singapore [semi.org]<br />

May 29-June 1 ECTC 2007: 57th<br />

Electronics Components and<br />

Technology Conference, Reno, Nev.<br />

[ectc.net]<br />

JUNE<br />

4-6 IEEE 2007 International<br />

Interconnect Technology Conference,<br />

Burlingame, Calif. [ieee.org]<br />

13-15 PEAKS Symposium on<br />

Advanced Cleaning Technology,<br />

Whitefish, Mont. [semitool.com/peaks]<br />

JULY<br />

SEMICON West<br />

16-20 (Conference), 17-19 (Exhibits),<br />

Moscone Center, San Francisco<br />

[semi.org]<br />

Simtek Corp. Hires Hulse for Worldwide Marketing Post<br />

Colorado Springs, Colo.—Grant Hulse<br />

has joined Simtek Corp., a provider of<br />

nonvolatile SRAMs, as vice president of<br />

worldwide marketing. He joined the<br />

company from Qualcomm, where he<br />

was an RF product line manager.<br />

Hulse reports to Simtek president<br />

Harold Blomquist, and will be based in<br />

Launch your<br />

new flip-chip<br />

product in<br />

record time.<br />

assembly in BGA, ceramic, plastic,<br />

QFN, COB and MCM packages.<br />

In addition to flip-chip capability,<br />

CORWIL has outstanding wirebonding<br />

expertise for ultra-fine pitch applications<br />

in gold and aluminum wire.<br />

Contact Us At:<br />

CORWIL Technology Corporation<br />

1635 McCarthy Blvd.<br />

Milpitas, CA 95035 info@corwil.com<br />

Tel: 408-321-6404 www.corwil.com<br />

Fax: 408-321-6407 ISO 9001:2000 Registered<br />

the company’s San Diego office. He<br />

received a master’s degree in electrical<br />

engineering from Stanford University.<br />

[simtek.com]<br />

Did You Know? <strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong><br />

is now offered in a digital format with a<br />

powerful search engine!<br />

COMPLEX FLIP-CHIP<br />

ASSEMBLY WITH<br />

SAME DAY TURN<br />

➢ Over 3200 bump/ball IO’s<br />

➢ Flexible Process Flows<br />

➢ Wide Material Selection<br />

➢ Gold Stud Bumping<br />

➢ Prototypes: as quick as<br />

8 hours!<br />

➢ Production: 1000’s of<br />

units per week<br />

CORWIL has developed into the premier<br />

U.S.-based packaging subcontractor with<br />

world-class wafer thinning, dicing, pick-andplace<br />

and visual<br />

inspection, plus<br />

state-of-the-art IC<br />

Since 1990 CORWIL has built its reputation providing customers with:<br />

Excellent Quality and Superior Service<br />

DSCC QML Certification<br />

MIL-PRF-38535<br />

MIL-STD-883<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ March 2007 ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 21

INDUSTRY NEWS<br />

SEMICONDUCTORS AND THE LAW<br />

TI Did Not Infringe Patent for DSPs, U.S. District Court Rules<br />

Dallas—Texas Instruments did not<br />

infringe a digital signal processor patent,<br />

according to a ruling by the U.S. District<br />

Court for the Central District of California.<br />

The Court granted a summary judgment<br />

for TI in ruling against a suit brought<br />

Micro-volume dispensing requires three core<br />

technologies. Without them, you can forget<br />

about accurate volumes and placement:<br />

by Microprocessor Enhancement<br />

Corp. (MEC), a subsidiary of Acacia<br />

Research Corp., Newport Beach, Calif.<br />

MEC was seeking more than $94 million<br />

and a permanent injunction<br />

against TI’s C6000 DSP platform. The<br />

THERE ARE NO SHORTCUTS<br />

TO A 5-MIL DOT<br />

Court also ordered MEC to pay TI’s<br />

court costs.<br />

MEC filed suit against both Intel<br />

Corp. and TI in April 2005, alleging<br />

patent infringement by Intel’s Itanium<br />

microprocessors and certain DSPs sold<br />

by TI. The Intel litigation is still pending.<br />

The MEC patents relate to an architecture<br />

employed in advanced pipeline<br />

processors. This architecture enables<br />

conditional execution of processor<br />

instructions and a whether the instructions<br />

should be written back to memory.<br />

By conditionally executing instructions,<br />

according to MEC, the processors gain<br />

significant improvements in speed.<br />

[acaciaresearch.com] [ti.com]<br />

• DL Micro Valve with brushless<br />

servo motor dispenses micro<br />

volumes of material in precise,<br />

repeatable patterns.<br />

• DL carbide auger and cartridge<br />

combine for exceptional material<br />

flow. Easily extracted for<br />

rapid cleaning.<br />

For dot sizes less than 10-mil, there is one<br />

product line that is proven and trusted –<br />

by manufacturers in semiconductor packaging,<br />

electronics assembly, medical device, and<br />

electro-mechanical assembly the world over.<br />

R<br />

• DL custom dispensing needles<br />

precision machined from<br />

solid stainless steel.<br />

Conically chamfered tip<br />

facilitates material release.<br />

216 River Street<br />

Haverhill, MA 01832 USA<br />

Phone: 978-374-6451<br />

Fax: 978-372-4889<br />

www.dltechnology.com<br />

Micro Valve is a trademark of DL Technology LLC. DL Technology is a registered trademark of DL Technology LLC.<br />

Dr. Mackie Joins Indium<br />

As Semi Product Manager<br />

Clinton, N.Y.—Dr.<br />

Andy Mackie has<br />

joined the Indium<br />

Corp. of America as<br />

product manager for<br />

semiconductor<br />

packaging materials,<br />

based at the company’s<br />

Dr. Andy Mackie Clinton headquarters.<br />

Dr. Mackie brings<br />

more than 17 years of experience in new<br />

product development, sales, and marketing<br />

of electronics assembly and semiconductor<br />

packaging to the company.<br />

He received the IPC President’s<br />

Award in 2001 for his leadership in<br />

IPC’s Solder Paste Task Force and the<br />

Assembly and Joining Materials<br />

Subcommittee.<br />

He holds a Ph. D. in physical chemistry<br />

from the University of Nottingham,<br />

England, and a master’s degree in surface<br />

and colloid chemistry from the University<br />

of Bristol, England. [indium.com]<br />

www.chipscalereview.com<br />

22<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ March 2007 ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

INDUSTRY NEWS<br />

Packaging Industry Veteran Opens Technical Sales Firm<br />

From left, Augustine Yap, Cristel Technologies; Takehiko Murakami, Minami; Yoshihiro Shimada of PacVision<br />

Corp., Japanese rep for Minami and PTA; Danny Fields; S.Y. Lee and Celina See, both of PTA.<br />

San Jose—Danny Fields, a 20-year<br />

veteran of the semiconductor packaging<br />

<strong>industry</strong>, has founded Pacific Gate<br />

Technologies, a technical sales firm.<br />

For nearly a decade, Fields was sales<br />

director for IPAC/i2a, San Jose, a<br />

provider of advanced semiconductor<br />

packaging and test.<br />

He earlier held similar titles and posts<br />

at AIS and AME/IMI, semiconductor<br />

assembly vendors offshore.<br />

Pacific Gate’s initial clients are Minami<br />

of Fuchu City, Japan [ho-minami.co.jp],<br />

a maker of screen printing and reflow<br />

systems for surface mount and device<br />

packaging; and PTA [polarta.com],a<br />

provider of IC assembly services based<br />

in Penang, Malaysia.<br />

Minami offers a low-cost screen<br />

printing system for wafer-level CSPs,<br />

with ball diameters ranging from 95 to<br />

500 microns. [pacgate-us.com]<br />

Silicon Nanowire Biochip Will Speed Genetic Tests<br />

Singapore—A new, highly sensitive<br />

biochip, based on silicon nanowire technology,<br />

will revolutionize the detection<br />

and analysis of RNA and DNA, according<br />

to its developers.<br />

The biochip will be produced through<br />

the combined efforts of Singapore’s<br />

Institute of Microelectronics (IME),<br />

Australian-based Bio<strong>Chip</strong> Innovations<br />

and SiMEMS, also of Singapore.<br />

The biochip, according to the developers,<br />

will shorten the time for genetic<br />

testing by directly detecting single DNA<br />

or RNA molecules. Because of their<br />

nanometer scale, silicon nanowires<br />

enable a greater sensitivity of detection.<br />

The nanowires can also detect biomarkers<br />

and other bio-molecules such<br />

as bacterial, viral and other specific<br />

genetic sequences.<br />

Uppili Raghavan, SiMEMS CEO, says<br />

most biochip systems now in use or<br />

IME is developing a nanowire biochip in a joint program<br />

with an Australian and Singaporean company.<br />

under development employ complex<br />

and expensive optics, signal processing<br />

systems and data interpretation, “all of<br />

which are impediments to adoption by<br />

the diagnostics <strong>industry</strong>.”<br />

The nanowire devices can be manufactured<br />

in standard CMOS silicon<br />

foundries, allowing them to be mass<br />

produced “reliably and cost-effectively,”<br />

Raghavan says.<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ March 2007 ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 23

INDUSTRY NEWS<br />

Mirrored Pinouts Continued from page 13 >><br />

Invention Donated<br />

However, last year inventor Charles S.<br />

Clark, the father of two Liberty University<br />

alumni, and a 30-year veteran of the electronics<br />

<strong>industry</strong>, donated his invention<br />

for “mirrored pinouts” to the university.<br />

Martin “Marty”<br />

Hart, meanwhile, is<br />

a veteran of the<br />

semiconductor<br />

<strong>industry</strong> and the<br />

“King of Dummy<br />

Components,” which<br />

he has purveyed for<br />

Martin Hart several decades<br />

through his Garden<br />

Grove, Calif., company, TopLine<br />

[topline.tv]<br />

Liberty, with no experience in semiconductors<br />

or electronics, decided it<br />

needed a way to bring Clark’s invention<br />

to market. The university took a booth<br />

at last year’s PCB West, hoping<br />

to interest someone with experience<br />

and connections.<br />

Hart was drawn to the<br />

Liberty booth at the show and<br />

discussed the invention with<br />

Clark, he told <strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong><br />

recently at APEX in Los<br />

Angeles. When Clark explained<br />

it, says Hart, “I realized that my<br />

life would not be the same again.”<br />

Letter of Intent Signed<br />

As a result of the meeting,<br />

Liberty has signed a letter of intent with<br />

Hart to take the mirrored pinout from<br />

concept to production. Liberty has also<br />

filed a patent for the invention and<br />

believes it may be worth “many, many<br />

millions of dollars.” Hart agrees.<br />

The benefits of the mirrored pinouts<br />

are a smaller circuit board, a faster circuit<br />

speed, reduction of inner layers (for<br />

U1<br />

Standard<br />

Pinout Pin 1<br />

Pin 1<br />

A<br />

B<br />

A ~ B = 20mm<br />

U1=Standard Pinout<br />

U2=Mirrored Pinout<br />

Mount same side of board.<br />

U2<br />

Mirrored<br />

Pinout<br />

This graphic shows the very short routing, 20mm in this case,<br />

between a standard pinout and a mirrored pinout on a board.<br />

reduced EMI), and lower cost. With a<br />

standard pinout, the circuit routing is<br />

relatively long. By combining standard<br />

pinout ICs together with mirrored<br />

pinout devices, however, the routing<br />

distance is very short, as shown in the<br />

illustration.<br />

The project has been taken over by<br />

Continued on page 25 >><br />

24<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ March 2007 ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

INDUSTRY NEWS<br />

Mirrored Pinouts Continued from page 24 >><br />

Hart’s startup, Mirror Semiconductor<br />

[mirrorsemi.com]. He’s in the very early<br />

stages of proof of concept, and is talking<br />

to prototype shops like Corwil. He<br />

believes as many as 20 percent of the<br />

boards currently built may ultimately<br />

have a small percentage of devices with<br />

mirrored pinouts on them.<br />

Most of the same IC assembly equipment<br />

used traditionally will be<br />

employed for the mirrored pinouts<br />

(MPs), except that MP packages are<br />

wirebonded in a clockwise direction,<br />

while standard pinouts are wirebonded<br />

in a counter-clockwise direction. Hart<br />

says he’s also considering deploying<br />

Microbond’s “Xwire” for bonding.<br />

New Software<br />

The greatest change in the IC device<br />

assembly process, he says, will involve<br />

designing new wire bonding software,<br />

and special fixtures will also be needed.<br />

“If the market will embrace MPs,” he<br />

adds, “we’re looking at capturing six billion<br />

devices that are now being packaged<br />

per year, which is only 5 percent of the<br />

total number of packages.”<br />

Part of the anticipated business, says<br />

Hart, will be as a fabless IC maker,<br />

delivering IC devices using the MPs.<br />

The other part of Mirror Semi’s revenue,<br />

he adds, will come from customers<br />

who want to license the technology,<br />

such as packaging foundries, OEMs,<br />

ODMs and other fabless IC makers.<br />

Essentially, any semiconductor can be<br />

made into a package with a mirrored<br />

pinout, and the MPs, known by the<br />

trademark “Mirror<strong>Chip</strong>s,” can be mixed<br />

on the same board with standard pinouts.<br />

Based in Irvine, Calif.<br />

The startup will be based in Irvine,<br />

Calif., near but separate from TopLine’s<br />

Southern California home. Hart says he<br />

has already lined-up representative<br />

offices in France, Germany, Japan,<br />

Korea, Sweden and the U.S.<br />

“We are now looking for both strategic<br />

partners and venture capitalists,”<br />

Hart says. If the MP is the success he<br />

believes it will be, Hart plans to “pick a<br />

successor for TopLine.”<br />

While he believes the first key application<br />

may be for parallel data bus circuits,<br />

the MP could have extensive<br />

applications for many devices, including<br />

microcontrollers, memory ICs and digital<br />

signal processors. ■ –Ron Iscoff, Editor<br />

‘Big 10’ OEMs Accounted for $84 Billion of <strong>Chip</strong>s Consumed<br />

Stamford, Conn.—The top 10 OEMs<br />

accounted for $84 billion of the semiconductor<br />

market in 2006. This figure<br />

represents one-third of all semiconductors<br />

consumed, according to <strong>industry</strong><br />

analyst Gartner Inc.<br />

This figure represents a 9 percent<br />

increase from 2005, when the top 10<br />

OEMs accounted for $77 billion of<br />

semiconductor sales.<br />

HP was the biggest chip consumer<br />

with about $12 billion, but Nokia and<br />

Dell closed to within $0.5 billion.<br />

Samsung and Sony completed the top<br />

five, followed by Motorola, Siemens,<br />

Toshiba, LG and Apple Computer.<br />

According to Alfonso Velosa,<br />

Top 10 OEM Semiconductor Consumption,<br />

2005-2006 (Billions of Dollars)<br />

Company 2006 2005<br />

HP $12 $12<br />

Nokia $12 $10<br />

Dell $12 $11<br />

Samsung $9 $8<br />

Sony $9 $9<br />

Motorola $8 $7<br />

Siemens $8 $7<br />

Toshiba $5 $5<br />

LG $4 $4<br />

Apple $4 $4<br />

(Source: Gartner Dataquest, Jan. 2007)<br />

Gartner’s research director, “Data processing<br />

and telecommunications firms<br />

represented 75 percent of the total<br />

semiconductor spending by the top<br />

consumers.” [gartner.com]<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ March 2007 ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 25

INDUSTRY NEWS<br />

APEX Continued from page 15 >><br />

Here’s a recap of locations and dates,<br />

in case you are now keeping score:<br />

Year Location Date (Exhibits)<br />

2000 Long Beach March 12-16<br />

2001 San Diego January 16-18<br />

2002 San Diego January 22-24<br />

2003 Anaheim March 31-April 2<br />

2004 Anaheim February 24-26<br />

2005 Anaheim February 24-26<br />

2007 Los Angeles February 20-22<br />

2008 Los Angeles February 19-21<br />

We think the hallmark of a good<br />

event is to keep a similar date and location.<br />

After every change in venue, there<br />

is a learning curve for the sponsor, for<br />

the exhibitors and for the visitors.<br />

The only venue that APEX has booked<br />

long enough to overcome that curve was in<br />

Anaheim. Now we’ve begun climbing up<br />

the learning curve again. Yes, we realize<br />

that the Anaheim Convention Center<br />

told the IPC not to return because the<br />

show didn’t bring in enough money.<br />

A Fizzler<br />

As it turned out, Intel Corp. took over the<br />

Anaheim dates for an event that reportedly<br />

fizzled.<br />

After stumbling around dates for five<br />

years, finally, in 2005 it appeared IPC had<br />

finally locked into mid-February. Now if<br />

they can only keep the same location!<br />

The rarely lamented NEPCON West<br />

show kept virtually the same dates<br />

(beginning of March) and same location<br />

(Anaheim Convention Center) for nearly<br />

all of its 30 plus years.<br />

That said, the Los Angeles Convention<br />

Center didn’t turn out to be as bad a choice<br />

as we expected. Downtown L.A. has<br />

undergone a renaissance over the past<br />

few years and the Convention Center is<br />

a major beneficiary of gentrification.<br />

Wandering Around<br />

We complained loudly about the lack of<br />

proper signage directing us to the show.<br />

Although the IPC shows only used one<br />

large hall, the LACC has four of them, with<br />

directional names. We were wandering<br />

around West Hall (visions of SEMICON<br />

West!) for 10 minutes before realizing the<br />

show was in South Hall (or was it North Hall)!<br />

My pal, Joe Marcello, a retired veteran<br />

of the semiconductor packaging <strong>industry</strong><br />

and attendee/speaker/exhibitor at<br />

zillions of trade shows in almost every<br />

niche of the world, barked to me,<br />

“They’d never get away with this lack of<br />

signage in Europe, Ron!”<br />

Keynoter astronaut Buzz Aldrin describes his<br />

space flight while IPC captures the moments on<br />

video. Joseph Fjelstad is at Dr. Aldrin’s left.<br />

In fact, poor signage, while it seems a<br />

simple matter that I have already spent<br />

too many words on, has been one of the<br />

chief complaints at SEMICON West<br />

every year! It’s typically these little<br />

annoyances that people remember.<br />

In addition to exhibits, of course, were<br />

the technical papers and the keynotes.<br />

The celebrity speaker was astronaut Dr.<br />

“Buzz” Aldrin.<br />

We understand it costs about $30,000<br />

to hire Buzz as your speaker. Perhaps the<br />

IPC could have spent a few of those dollars<br />

on signage and gotten someone<br />

closer to the electronics <strong>industry</strong> as the<br />

keynote for a few dollars less, or free. ■<br />

F&K Delvotec North America, 27182 Burbank<br />

Foothill Ranch, CA 92610, phone 949/595-2200, fax 949/595-2207<br />

26<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ March 2007 ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

P O L Y M E R I N F U S E D M E T A L S Q U E E G E E S<br />

Maximize Your<br />

Micro-Electronics<br />

Printing Results<br />

From the Beginning, one company has<br />

championed the metal squeegee business<br />

like no other.<br />

Transition Automation founded modern<br />

fine pitch printing back in the early days<br />

when most SMT printers came with a rubber<br />

squeegee installed.<br />

Our customer successes<br />

have enabled us to<br />

continue to increase<br />

value and performance<br />

for end user printing<br />

applications.<br />

101 Billerica Avenue, Bldg 5<br />

N Billerica, Massachusetts 01862<br />

All Permalex Products are Guaranteed<br />

WEB: WWW.PERMALEX.COM<br />

PH: 800-648-3338 FX: ...-2300<br />

SALES@TRANSITIONAUTOMATION.COM

Are Wire Bonders Running Out of Steam? How this<br />

Essential IC Assembly Tool Is Keeping Pace<br />

Unlike this venerable old steam-driven train, wire bonders have undergone constant improvement over the past 50 years.<br />

Wire bonders are becoming smarter, faster and more cost-effective on<br />

the assembly line. In the bonder’s 50+ year history, the machines have<br />

become not only the icon for IC assembly, but the most-needed tool at<br />

every IC assembler. Is there room for improvement? Of course, and<br />

we’ll explore that topic in this article.<br />

By Ron Iscoff, Editor<br />

[chipscale@gmail.com]<br />

We are gathered here today<br />

on this field of honor to<br />

commemorate, to celebrate and to<br />

memorialize the outstanding role<br />

played in the semiconductor assembly<br />

<strong>industry</strong> by wire bonders.<br />

We will long remember (nor soon<br />

forget) the row upon row of automatic<br />

wire bonders that were the<br />

stuff of almost every semiconductor<br />

assembler from Amkor to STATS<br />

<strong>Chip</strong>PAC.<br />

28<br />

<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ March 2007 ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

Even though they have been replaced<br />

by processes that package our integrated<br />

circuits at locations several million light<br />

years from our earth, and at a speed and<br />

pitch that boggle the mind, the venerable<br />

wire bonder deserves much credit for<br />