Full-Custom Analog IC Design using Cadence DFII Virtuoso/Assura

Full-Custom Analog IC Design using Cadence DFII Virtuoso/Assura

Full-Custom Analog IC Design using Cadence DFII Virtuoso/Assura

- No tags were found...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

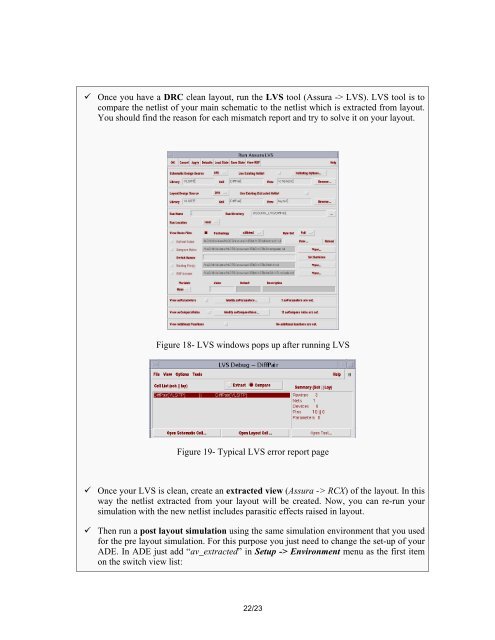

Once you have a DRC clean layout, run the LVS tool (<strong>Assura</strong> -> LVS). LVS tool is tocompare the netlist of your main schematic to the netlist which is extracted from layout.You should find the reason for each mismatch report and try to solve it on your layout.Figure 18- LVS windows pops up after running LVSFigure 19- Typical LVS error report page Once your LVS is clean, create an extracted view (<strong>Assura</strong> -> RCX) of the layout. In thisway the netlist extracted from your layout will be created. Now, you can re-run yoursimulation with the new netlist includes parasitic effects raised in layout. Then run a post layout simulation <strong>using</strong> the same simulation environment that you usedfor the pre layout simulation. For this purpose you just need to change the set-up of yourADE. In ADE just add “av_extracted” in Setup -> Environment menu as the first itemon the switch view list:22/23