Test Cost

Test Cost

Test Cost

- No tags were found...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

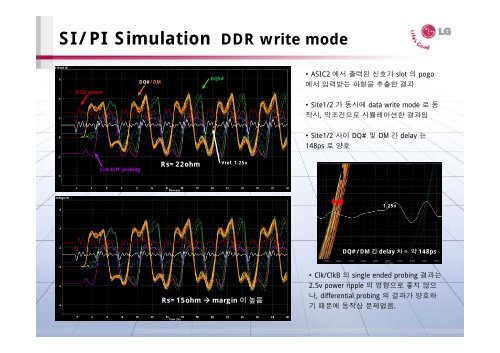

SI/PI Simulation DDR write mode2.5V powerDQ#/DMDQS#•ASIC2 에서 출력된 신호가 slot 의 pogo에서 입력받는 파형을 추출한 결과•Site1/2 가 동시에 data write mode 로 동작시, 악조건으로 시뮬레이션한 결과임• Site1/2 사이 DQ# 및 DM 간 delay 는148ps 로양호CLK Diff. probingRs=22ohmVref. 1.25v1.25vDQ#/DM 간 delay 차 = 약 148psRs=15ohm margin 이 높음• Clk/ClkB 의 single ended probing 결과는2.5v power ripple 의 영향으로 좋지 않으나, differential probing 의 결과가 양호하기 때문에 동작상 문제없음.