Buffering in the Layout Environment - Computer Engineering ...

Buffering in the Layout Environment - Computer Engineering ...

Buffering in the Layout Environment - Computer Engineering ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

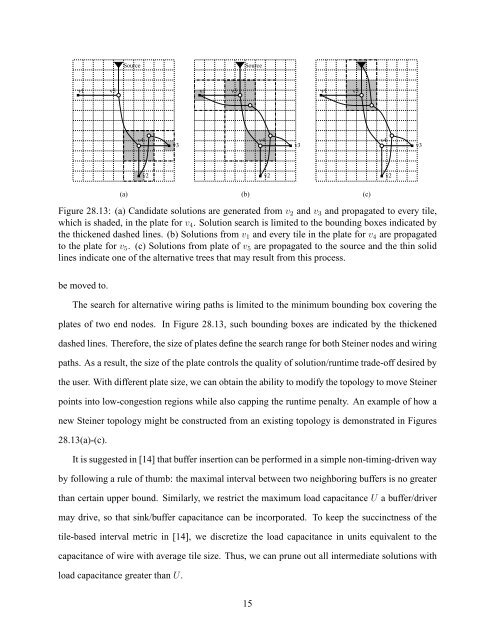

SourceSourcev1v5v1v5v1v5v4v3v4v3v4v3v2v2v2(a) (b) (c)Figure 28.13: (a) Candidate solutions are generated from v 2 and v 3 and propagated to every tile,which is shaded, <strong>in</strong> <strong>the</strong> plate for v 4 . Solution search is limited to <strong>the</strong> bound<strong>in</strong>g boxes <strong>in</strong>dicated by<strong>the</strong> thickened dashed l<strong>in</strong>es. (b) Solutions from v 1 and every tile <strong>in</strong> <strong>the</strong> plate for v 4 are propagatedto <strong>the</strong> plate for v 5 . (c) Solutions from plate of v 5 are propagated to <strong>the</strong> source and <strong>the</strong> th<strong>in</strong> solidl<strong>in</strong>es <strong>in</strong>dicate one of <strong>the</strong> alternative trees that may result from this process.be moved to.The search for alternative wir<strong>in</strong>g paths is limited to <strong>the</strong> m<strong>in</strong>imum bound<strong>in</strong>g box cover<strong>in</strong>g <strong>the</strong>plates of two end nodes. In Figure 28.13, such bound<strong>in</strong>g boxes are <strong>in</strong>dicated by <strong>the</strong> thickeneddashed l<strong>in</strong>es. Therefore, <strong>the</strong> size of plates def<strong>in</strong>e <strong>the</strong> search range for both Ste<strong>in</strong>er nodes and wir<strong>in</strong>gpaths. As a result, <strong>the</strong> size of <strong>the</strong> plate controls <strong>the</strong> quality of solution/runtime trade-off desired by<strong>the</strong> user. With different plate size, we can obta<strong>in</strong> <strong>the</strong> ability to modify <strong>the</strong> topology to move Ste<strong>in</strong>erpo<strong>in</strong>ts <strong>in</strong>to low-congestion regions while also capp<strong>in</strong>g <strong>the</strong> runtime penalty. An example of how anew Ste<strong>in</strong>er topology might be constructed from an exist<strong>in</strong>g topology is demonstrated <strong>in</strong> Figures28.13(a)-(c).It is suggested <strong>in</strong> [14] that buffer <strong>in</strong>sertion can be performed <strong>in</strong> a simple non-tim<strong>in</strong>g-driven wayby follow<strong>in</strong>g a rule of thumb: <strong>the</strong> maximal <strong>in</strong>terval between two neighbor<strong>in</strong>g buffers is no greaterthan certa<strong>in</strong> upper bound. Similarly, we restrict <strong>the</strong> maximum load capacitance U a buffer/drivermay drive, so that s<strong>in</strong>k/buffer capacitance can be <strong>in</strong>corporated. To keep <strong>the</strong> succ<strong>in</strong>ctness of <strong>the</strong>tile-based <strong>in</strong>terval metric <strong>in</strong> [14], we discretize <strong>the</strong> load capacitance <strong>in</strong> units equivalent to <strong>the</strong>capacitance of wire with average tile size. Thus, we can prune out all <strong>in</strong>termediate solutions withload capacitance greater than U.15