Eric Vittoz - IEEE

Eric Vittoz - IEEE

Eric Vittoz - IEEE

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

TECHNICAL LITERATURE<br />

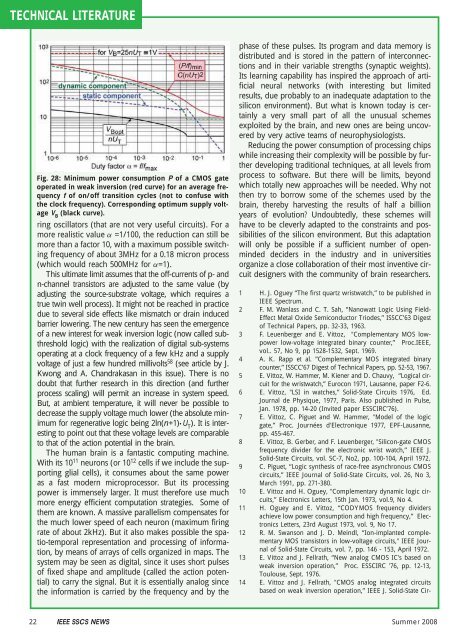

Fig. 28: Minimum power consumption P of a CMOS gate<br />

operated in weak inversion (red curve) for an average frequency<br />

f of on/off transition cycles (not to confuse with<br />

the clock frequency). Corresponding optimum supply voltage<br />

V B (black curve).<br />

ring oscillators (that are not very useful circuits). For a<br />

more realistic value α =1/100, the reduction can still be<br />

more than a factor 10, with a maximum possible switching<br />

frequency of about 3MHz for a 0.18 micron process<br />

(which would reach 500MHz for α=1).<br />

This ultimate limit assumes that the off-currents of p- and<br />

n-channel transistors are adjusted to the same value (by<br />

adjusting the source-substrate voltage, which requires a<br />

true twin well process). It might not be reached in practice<br />

due to several side effects like mismatch or drain induced<br />

barrier lowering. The new century has seen the emergence<br />

of a new interest for weak inversion logic (now called subthreshold<br />

logic) with the realization of digital sub-systems<br />

operating at a clock frequency of a few kHz and a supply<br />

voltage of just a few hundred millivolts 58 (see article by J.<br />

Kwong and A. Chandrakasan in this issue). There is no<br />

doubt that further research in this direction (and further<br />

process scaling) will permit an increase in system speed.<br />

But, at ambient temperature, it will never be possible to<br />

decrease the supply voltage much lower (the absolute minimum<br />

for regenerative logic being 2ln(n+1)•U T ). It is interesting<br />

to point out that these voltage levels are comparable<br />

to that of the action potential in the brain.<br />

The human brain is a fantastic computing machine.<br />

With its 10 11 neurons (or 10 12 cells if we include the supporting<br />

glial cells), it consumes about the same power<br />

as a fast modern microprocessor. But its processing<br />

power is immensely larger. It must therefore use much<br />

more energy efficient computation strategies. Some of<br />

them are known. A massive parallelism compensates for<br />

the much lower speed of each neuron (maximum firing<br />

rate of about 2kHz). But it also makes possible the spatio-temporal<br />

representation and processing of information,<br />

by means of arrays of cells organized in maps. The<br />

system may be seen as digital, since it uses short pulses<br />

of fixed shape and amplitude (called the action potential)<br />

to carry the signal. But it is essentially analog since<br />

the information is carried by the frequency and by the<br />

phase of these pulses. Its program and data memory is<br />

distributed and is stored in the pattern of interconnections<br />

and in their variable strengths (synaptic weights).<br />

Its learning capability has inspired the approach of artificial<br />

neural networks (with interesting but limited<br />

results, due probably to an inadequate adaptation to the<br />

silicon environment). But what is known today is certainly<br />

a very small part of all the unusual schemes<br />

exploited by the brain, and new ones are being uncovered<br />

by very active teams of neurophysiologists.<br />

Reducing the power consumption of processing chips<br />

while increasing their complexity will be possible by further<br />

developing traditional techniques, at all levels from<br />

process to software. But there will be limits, beyond<br />

which totally new approaches will be needed. Why not<br />

then try to borrow some of the schemes used by the<br />

brain, thereby harvesting the results of half a billion<br />

years of evolution? Undoubtedly, these schemes will<br />

have to be cleverly adapted to the constraints and possibilities<br />

of the silicon environment. But this adaptation<br />

will only be possible if a sufficient number of openminded<br />

deciders in the industry and in universities<br />

organize a close collaboration of their most inventive circuit<br />

designers with the community of brain researchers.<br />

1 H. J. Oguey “The first quartz wristwatch,” to be published in<br />

<strong>IEEE</strong> Spectrum.<br />

2 F. M. Wanlass and C. T. Sah, “Nanowatt Logic Using Field-<br />

Effect Metal Oxide Semiconductor Triodes,” ISSCC’63 Digest<br />

of Technical Papers, pp. 32-33, 1963.<br />

3 F. Leuenberger and E. <strong>Vittoz</strong>, "Complementary MOS lowpower<br />

low-voltage integrated binary counter,” Proc.<strong>IEEE</strong>,<br />

vol.. 57, No 9, pp 1528-1532, Sept. 1969.<br />

4 A. K. Rapp et al. ”Complementary MOS integrated binary<br />

counter,” ISSCC’67 Digest of Technical Papers, pp. 52-53, 1967.<br />

5 E. <strong>Vittoz</strong>, W. Hammer, M. Kiener and D. Chauvy, “Logical circuit<br />

for the wristwatch,” Eurocon 1971, Lausanne, paper F2-6.<br />

6 E. <strong>Vittoz</strong>, "LSI in watches,” Solid-State Circuits 1976, Ed.<br />

Journal de Physique, 1977, Paris. Also published in Pulse,<br />

Jan. 1978, pp. 14-20 (Invited paper ESSCIRC’76).<br />

7 E. <strong>Vittoz</strong>, C. Piguet and W. Hammer, "Model of the logic<br />

gate,” Proc. Journées d'Electronique 1977, EPF-Lausanne,<br />

pp. 455-467.<br />

8 E. <strong>Vittoz</strong>, B. Gerber, and F. Leuenberger, "Silicon-gate CMOS<br />

frequency divider for the electronic wrist watch,” <strong>IEEE</strong> J.<br />

Solid-State Circuits, vol. SC-7, No2, pp. 100-104, April 1972.<br />

9 C. Piguet, “Logic synthesis of race-free asynchronous CMOS<br />

circuits,” <strong>IEEE</strong> Journal of Solid-State Circuits, vol. 26, No 3,<br />

March 1991, pp. 271-380.<br />

10 E. <strong>Vittoz</strong> and H. Oguey, "Complementary dynamic logic circuits,”<br />

Electronics Letters, 15th Jan. 1973, vol.9, No 4.<br />

11 H. Oguey and E. <strong>Vittoz</strong>, “CODYMOS frequency dividers<br />

achieve low power consumption and high frequency,” Electronics<br />

Letters, 23rd August 1973, vol. 9, No 17.<br />

12 R. M. Swanson and J. D. Meindl, “Ion-implanted complementary<br />

MOS transistors in low-voltage circuits," <strong>IEEE</strong> Journal<br />

of Solid-State Circuits, vol. 7, pp. 146 - 153, April 1972.<br />

13 E. <strong>Vittoz</strong> and J. Fellrath, “New analog CMOS IC's based on<br />

weak inversion operation,” Proc. ESSCIRC '76, pp. 12-13,<br />

Toulouse, Sept. 1976.<br />

14 E. <strong>Vittoz</strong> and J. Fellrath, "CMOS analog integrated circuits<br />

based on weak inversion operation,” <strong>IEEE</strong> J. Solid-State Cir-<br />

22 <strong>IEEE</strong> SSCS NEWS Summer 2008