Eric Vittoz - IEEE

Eric Vittoz - IEEE

Eric Vittoz - IEEE

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

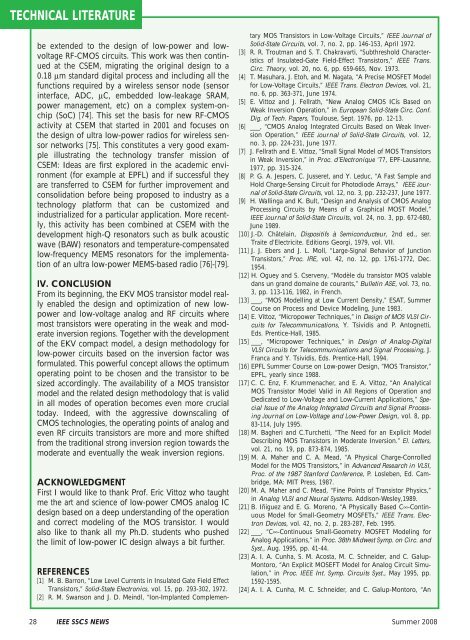

TECHNICAL LITERATURE<br />

be extended to the design of low-power and lowvoltage<br />

RF-CMOS circuits. This work was then continued<br />

at the CSEM, migrating the original design to a<br />

0.18 μm standard digital process and including all the<br />

functions required by a wireless sensor node (sensor<br />

interface, ADC, μC, embedded low-leakage SRAM,<br />

power management, etc) on a complex system-onchip<br />

(SoC) [74]. This set the basis for new RF-CMOS<br />

activity at CSEM that started in 2001 and focuses on<br />

the design of ultra low-power radios for wireless sensor<br />

networks [75]. This constitutes a very good example<br />

illustrating the technology transfer mission of<br />

CSEM: Ideas are first explored in the academic environment<br />

(for example at EPFL) and if successful they<br />

are transferred to CSEM for further improvement and<br />

consolidation before being proposed to industry as a<br />

technology platform that can be customized and<br />

industrialized for a particular application. More recently,<br />

this activity has been combined at CSEM with the<br />

development high-Q resonators such as bulk acoustic<br />

wave (BAW) resonators and temperature-compensated<br />

low-frequency MEMS resonators for the implementation<br />

of an ultra low-power MEMS-based radio [76]-[79].<br />

IV. CONCLUSION<br />

From its beginning, the EKV MOS transistor model really<br />

enabled the design and optimization of new lowpower<br />

and low-voltage analog and RF circuits where<br />

most transistors were operating in the weak and moderate<br />

inversion regions. Together with the development<br />

of the EKV compact model, a design methodology for<br />

low-power circuits based on the inversion factor was<br />

formulated. This powerful concept allows the optimum<br />

operating point to be chosen and the transistor to be<br />

sized accordingly. The availability of a MOS transistor<br />

model and the related design methodology that is valid<br />

in all modes of operation becomes even more crucial<br />

today. Indeed, with the aggressive downscaling of<br />

CMOS technologies, the operating points of analog and<br />

even RF circuits transistors are more and more shifted<br />

from the traditional strong inversion region towards the<br />

moderate and eventually the weak inversion regions.<br />

ACKNOWLEDGMENT<br />

First I would like to thank Prof. <strong>Eric</strong> <strong>Vittoz</strong> who taught<br />

me the art and science of low-power CMOS analog IC<br />

design based on a deep understanding of the operation<br />

and correct modeling of the MOS transistor. I would<br />

also like to thank all my Ph.D. students who pushed<br />

the limit of low-power IC design always a bit further.<br />

REFERENCES<br />

[1] M. B. Barron, “Low Level Currents in Insulated Gate Field Effect<br />

Transistors,” Solid-State Electronics, vol. 15, pp. 293-302, 1972.<br />

[2] R. M. Swanson and J. D. Meindl, “Ion-Implanted Complemen-<br />

tary MOS Transistors in Low-Voltage Circuits,” <strong>IEEE</strong> Journal of<br />

Solid-State Circuits, vol. 7, no. 2, pp. 146-153, April 1972.<br />

[3] R. R. Troutman and S. T. Chakravarti, “Subthreshold Characteristics<br />

of Insulated-Gate Field-Effect Transistors,” <strong>IEEE</strong> Trans.<br />

Circ. Theory, vol. 20, no. 6, pp. 659-665, Nov. 1973.<br />

[4] T. Masuhara, J. Etoh, and M. Nagata, “A Precise MOSFET Model<br />

for Low-Voltage Circuits,” <strong>IEEE</strong> Trans. Electron Devices, vol. 21,<br />

no. 6, pp. 363-371, June 1974.<br />

[5] E. <strong>Vittoz</strong> and J. Fellrath, “New Analog CMOS ICís Based on<br />

Weak Inversion Operation,” in European Solid-State Circ. Conf.<br />

Dig. of Tech. Papers, Toulouse, Sept. 1976, pp. 12-13.<br />

[6] ___, “CMOS Analog Integrated Circuits Based on Weak Inversion<br />

Operation,” <strong>IEEE</strong> Journal of Solid-State Circuits, vol. 12,<br />

no. 3, pp. 224-231, June 1977.<br />

[7] J. Fellrath and E. <strong>Vittoz</strong>, “Small Signal Model of MOS Transistors<br />

in Weak Inversion,” in Proc. d’Electronique ‘77, EPF-Lausanne,<br />

1977, pp. 315-324.<br />

[8] P. G. A. Jespers, C. Jusseret, and Y. Leduc, “A Fast Sample and<br />

Hold Charge-Sensing Circuit for Photodiode Arrays,” <strong>IEEE</strong> Journal<br />

of Solid-State Circuits, vol. 12, no. 3, pp. 232-237, June 1977.<br />

[9] H. Wallinga and K. Bult, “Design and Analysis of CMOS Analog<br />

Processing Circuits by Means of a Graphical MOST Model,”<br />

<strong>IEEE</strong> Journal of Solid-State Circuits, vol. 24, no. 3, pp. 672-680,<br />

June 1989.<br />

[10] J.-D. Châtelain, Dispositifs à Semiconducteur, 2nd ed., ser.<br />

Traite d’Electricite. Editions Georgi, 1979, vol. VII.<br />

[11] J. J. Ebers and J. L. Moll, “Large-Signal Behavior of Junction<br />

Transistors,” Proc. IRE, vol. 42, no. 12, pp. 1761-1772, Dec.<br />

1954.<br />

[12] H. Oguey and S. Cserveny, “Modèle du transistor MOS valable<br />

dans un grand domaine de courants,” Bulletin ASE, vol. 73, no.<br />

3, pp. 113-116, 1982, in French.<br />

[13] ___, “MOS Modelling at Low Current Density,” ESAT, Summer<br />

Course on Process and Device Modeling, June 1983.<br />

[14] E. <strong>Vittoz</strong>, “Micropower Techniques,” in Design of MOS VLSI Circuits<br />

for Telecommunications, Y. Tsividis and P. Antognetti,<br />

Eds. Prentice-Hall, 1985.<br />

[15] ___, “Micropower Techniques,” in Design of Analog-Digital<br />

VLSI Circuits for Telecommunications and Signal Processing, J.<br />

Franca and Y. Tsividis, Eds. Prentice-Hall, 1994.<br />

[16] EPFL Summer Course on Low-power Design, ”MOS Transistor,”<br />

EPFL, yearly since 1988.<br />

[17] C. C. Enz, F. Krummenacher, and E. A. <strong>Vittoz</strong>, “An Analytical<br />

MOS Transistor Model Valid in All Regions of Operation and<br />

Dedicated to Low-Voltage and Low-Current Applications,” Special<br />

Issue of the Analog Integrated Circuits and Signal Processing<br />

Journal on Low-Voltage and Low-Power Design, vol. 8, pp.<br />

83-114, July 1995.<br />

[18] M. Bagheri and C.Turchetti, “The Need for an Explicit Model<br />

Describing MOS Transistors in Moderate Inversion.” El. Letters,<br />

vol. 21, no. 19, pp. 873-874, 1985.<br />

[19] M. A. Maher and C. A. Mead, “A Physical Charge-Conrolled<br />

Model for the MOS Transistors,” in Advanced Research in VLSI,<br />

Proc. of the 1987 Stanford Conference, P. Losleben, Ed. Cambridge,<br />

MA: MIT Press, 1987.<br />

[20] M. A. Maher and C. Mead, “Fine Points of Transistor Physics,”<br />

in Analog VLSI and Neural Systems. Addison-Wesley,1989.<br />

[21] B. Iñiguez and E. G. Moreno, “A Physically Based C∞-Continuous<br />

Model for Small-Geometry MOSFETs,” <strong>IEEE</strong> Trans. Electron<br />

Devices, vol. 42, no. 2, p. 283-287, Feb. 1995.<br />

[22] ___, “C∞-Continuous Small-Geometry MOSFET Modeling for<br />

Analog Applications,” in Proc. 38th Midwest Symp. on Circ. and<br />

Syst., Aug. 1995, pp. 41-44.<br />

[23] A. I. A. Cunha, S. M. Acosta, M. C. Schneider, and C. Galup-<br />

Montoro, “An Explicit MOSEFT Model for Analog Circuit Simulation,”<br />

in Proc. <strong>IEEE</strong> Int. Symp. Circuits Syst., May 1995, pp.<br />

1592-1595.<br />

[24] A. I. A. Cunha, M. C. Schneider, and C. Galup-Montoro, “An<br />

28 <strong>IEEE</strong> SSCS NEWS Summer 2008