Multiplicación Secuencial en Dispositivos Lógicos Programables

Multiplicación Secuencial en Dispositivos Lógicos Programables

Multiplicación Secuencial en Dispositivos Lógicos Programables

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

MULTIPLICACIÓN SECUENCIAL EN<br />

DISPOSITIVOS L ÓGICOS<br />

PROGRAMABLES<br />

Ing. Marcos Funes<br />

Este Trabajo de Tesis fue pres<strong>en</strong>tado al Departam<strong>en</strong>to de Electrónica<br />

de la Facultad de Ing<strong>en</strong>iería de la Universidad Nacional de Mar del Plata<br />

el 8 de Octubre de 2007, como requisito parcial para la obt<strong>en</strong>ción del título de<br />

Doctor <strong>en</strong> Ing<strong>en</strong>iería. M<strong>en</strong>ción Electrónica<br />

Director: Dr. Daniel Carrica<br />

Co-Director: Ing. Mario B<strong>en</strong>edetti

A mis Padres.<br />

A Andrea.<br />

A Nicolás, Alejandro y Fernando

Índice g<strong>en</strong>eral<br />

Agradecimi<strong>en</strong>tos XVII<br />

Resum<strong>en</strong> XVIII<br />

Nom<strong>en</strong>clatura XX<br />

1. Introducción 1<br />

1.1. Estructuras de Multiplicadores . . . . . . . . . . . . . . . . . . . . 2<br />

1.2. Objetivos de la tesis . . . . . . . . . . . . . . . . . . . . . . . . . 4<br />

1.3. Organización de la tesis . . . . . . . . . . . . . . . . . . . . . . . 4<br />

2. Arquitecturas de Multiplicadores 6<br />

2.1. Introducción . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6<br />

2.2. Algoritmo de la <strong>Multiplicación</strong> . . . . . . . . . . . . . . . . . . . . 7<br />

2.2.1. Operandos <strong>en</strong> punto fijo . . . . . . . . . . . . . . . . . . . 7<br />

2.2.2. Operandos <strong>en</strong> punto flotante . . . . . . . . . . . . . . . . . 9<br />

2.3. Adición . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12<br />

2.3.1. Semisumador . . . . . . . . . . . . . . . . . . . . . . . . . 12<br />

2.3.2. Sumador Total . . . . . . . . . . . . . . . . . . . . . . . . 13<br />

2.3.3. Suma por Propagación de Acarreo . . . . . . . . . . . . . . 15<br />

2.3.4. Suma Carry-Save . . . . . . . . . . . . . . . . . . . . . . . 16<br />

iii

2.3.5. Suma Multi-operandos . . . . . . . . . . . . . . . . . . . . 17<br />

2.4. Multiplicadores Paralelos . . . . . . . . . . . . . . . . . . . . . . . 19<br />

2.4.1. Multiplicador por Tabla de Look-up . . . . . . . . . . . . . 19<br />

2.4.2. Multiplicador Ripple Carry . . . . . . . . . . . . . . . . . 20<br />

2.4.3. Multiplicador Carry Save . . . . . . . . . . . . . . . . . . . 22<br />

2.4.4. Multiplicador Guild . . . . . . . . . . . . . . . . . . . . . . 23<br />

2.4.5. Multipicador McCanny-McWhinter . . . . . . . . . . . . . 25<br />

2.5. Consumo de recursos lógicos . . . . . . . . . . . . . . . . . . . . . 25<br />

2.5.1. Operandos <strong>en</strong> Punto Fijo . . . . . . . . . . . . . . . . . . . 25<br />

2.5.2. Operandos <strong>en</strong> punto flotante . . . . . . . . . . . . . . . . . 31<br />

2.6. Conclusiones . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32<br />

3. Nuevas Arquitecturas de Multiplicadores 33<br />

3.1. Introducción . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33<br />

3.2. <strong>Multiplicación</strong> <strong>Secu<strong>en</strong>cial</strong> . . . . . . . . . . . . . . . . . . . . . . . 34<br />

3.2.1. Algoritmo . . . . . . . . . . . . . . . . . . . . . . . . . . . 34<br />

3.2.2. Implem<strong>en</strong>tación . . . . . . . . . . . . . . . . . . . . . . . . 37<br />

3.2.3. Multiplicador <strong>Secu<strong>en</strong>cial</strong> de Base 4 . . . . . . . . . . . . . 45<br />

3.3. Arquitecturas Propuestas <strong>en</strong> Punto Fijo . . . . . . . . . . . . . . 56<br />

3.3.1. Multiplicador <strong>Secu<strong>en</strong>cial</strong> Sin Entradas Registradas . . . . . 56<br />

3.3.2. Multiplicador <strong>Secu<strong>en</strong>cial</strong> Fraccionado . . . . . . . . . . . . 61<br />

3.3.3. Multiplicador de Sumas Consecutivas . . . . . . . . . . . . 67<br />

3.4. Comparación de los multiplicadores . . . . . . . . . . . . . . . . . 75<br />

3.4.1. Multiplicadores optimizados <strong>en</strong> consumo de recursos . . . . 75<br />

3.4.2. Multiplicadores optimizados <strong>en</strong> velocidad . . . . . . . . . . 76<br />

3.4.3. Performance de los multiplicadores . . . . . . . . . . . . . 78<br />

3.5. Arquitecturas Propuestas <strong>en</strong> Punto Flotante . . . . . . . . . . . . 80<br />

iv

3.5.1. Variante Multiplicador <strong>Secu<strong>en</strong>cial</strong> Sin Entradas Registradas 80<br />

3.5.2. Variante Multiplicador <strong>Secu<strong>en</strong>cial</strong> de Sumas Consecutivas . 86<br />

3.6. Conclusiones . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90<br />

4. Resultados Experim<strong>en</strong>tales 92<br />

4.1. Introducción . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92<br />

4.2. Parámetros de interés . . . . . . . . . . . . . . . . . . . . . . . . . 92<br />

4.3. <strong>Multiplicación</strong> <strong>en</strong> Punto Fijo . . . . . . . . . . . . . . . . . . . . . 93<br />

4.3.1. Consumo de recursos lógicos . . . . . . . . . . . . . . . . . 93<br />

4.3.2. Comportami<strong>en</strong>to temporal . . . . . . . . . . . . . . . . . . 98<br />

4.3.3. Comparación de los multiplicadores . . . . . . . . . . . . . 101<br />

4.4. <strong>Multiplicación</strong> <strong>en</strong> Punto Flotante . . . . . . . . . . . . . . . . . . 114<br />

4.4.1. Consumo de recursos lógicos . . . . . . . . . . . . . . . . . 114<br />

4.4.2. Comportami<strong>en</strong>to temporal . . . . . . . . . . . . . . . . . . 115<br />

4.4.3. Performance . . . . . . . . . . . . . . . . . . . . . . . . . . 116<br />

4.5. Conclusiones . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119<br />

5. Conclusiones 121<br />

5.0.1. Trabajos futuros . . . . . . . . . . . . . . . . . . . . . . . 127<br />

Bibliografía 129<br />

A. <strong>Dispositivos</strong> <strong>Lógicos</strong> <strong>Programables</strong> 137<br />

A.1. Introducción . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137<br />

A.2. PLD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138<br />

A.3. CPLD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139<br />

A.4. FPGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141<br />

A.4.1. Celdas Lógicas . . . . . . . . . . . . . . . . . . . . . . . . 143<br />

A.4.2. Recursos dedicados . . . . . . . . . . . . . . . . . . . . . . 145<br />

v

A.5. Conclusiones . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149<br />

B. Sistemas numéricos 150<br />

B.1. Introducción . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150<br />

B.2. Repres<strong>en</strong>tación numérica . . . . . . . . . . . . . . . . . . . . . . . 150<br />

B.2.1. Punto fijo . . . . . . . . . . . . . . . . . . . . . . . . . . . 151<br />

B.2.2. Punto flotante . . . . . . . . . . . . . . . . . . . . . . . . . 154<br />

B.2.3. No-conv<strong>en</strong>cionales . . . . . . . . . . . . . . . . . . . . . . . 157<br />

C. <strong>Multiplicación</strong> <strong>Secu<strong>en</strong>cial</strong> aplicada al Control de Movimi<strong>en</strong>to 159<br />

C.1. Introducción . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159<br />

C.2. Accionami<strong>en</strong>tos paso a paso . . . . . . . . . . . . . . . . . . . . . 161<br />

C.2.1. G<strong>en</strong>eración de perfiles de velocidad Off-line . . . . . . . . . 162<br />

C.2.2. G<strong>en</strong>eración de perfiles de velocidad On-line . . . . . . . . . 162<br />

C.3. G<strong>en</strong>eración de perfiles de velocidad mediante FPGA . . . . . . . . 167<br />

C.3.1. Implem<strong>en</strong>tación del producto Vr · nk . . . . . . . . . . . . 169<br />

C.4. Resultados experim<strong>en</strong>tales . . . . . . . . . . . . . . . . . . . . . . 172<br />

C.4.1. Modo de funcionami<strong>en</strong>to <strong>en</strong> pasos . . . . . . . . . . . . . . 172<br />

C.4.2. Modo de funcionami<strong>en</strong>to <strong>en</strong> micropasos . . . . . . . . . . . 174<br />

C.5. Conclusiones . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178<br />

D. Publicaciones 179<br />

D.1. Introducción . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179<br />

D.2. Multiplicadores secu<strong>en</strong>ciales <strong>en</strong> FPGA: Evaluación y Comparación<br />

de Parámetros . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181<br />

D.3. Estudio comparativo de multiplicadores secu<strong>en</strong>ciales implem<strong>en</strong>ta-<br />

dos <strong>en</strong> FPGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193<br />

D.4. Floating Point Multipliers with Reduced FPGA Area . . . . . . . 199<br />

vi

D.5. Performance Evaluation of FPGA Floating Point Multipliers . . . 207<br />

D.6. Novel FPGA based Floating Point Multiplier: Consecutive-Sums<br />

Sequ<strong>en</strong>tial Multiplier . . . . . . . . . . . . . . . . . . . . . . . . . 211<br />

D.7. Novel Stepper Motor Controller Based on FPGA Hardware Imple-<br />

m<strong>en</strong>tation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220<br />

D.8. FPGA based stepper motor controller . . . . . . . . . . . . . . . . 225<br />

vii

Índice de Tablas<br />

2.1. Producto de dos operandos de 4 bits . . . . . . . . . . . . . . . . 7<br />

2.2. Implem<strong>en</strong>tación de multiplicadores <strong>en</strong> FPGA. . . . . . . . . . . . 29<br />

3.1. Producto de dos operandos de 4 bits, acumulación de productos<br />

parciales. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34<br />

3.2. <strong>Multiplicación</strong> secu<strong>en</strong>cial con desplazami<strong>en</strong>to a la izquierda para<br />

operandos de 4 bits. . . . . . . . . . . . . . . . . . . . . . . . . . 35<br />

3.3. <strong>Multiplicación</strong> con desplazami<strong>en</strong>to a la derecha para operandos de<br />

4 bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36<br />

3.4. Estimación de consumo de recursos lógicos de un SM. . . . . . . . 40<br />

3.5. Retardos de una FPGA Xilinx Spartan-4. . . . . . . . . . . . . . . 43<br />

3.6. Producto de dos operandos <strong>en</strong> base 4 . . . . . . . . . . . . . . . . 46<br />

3.7. <strong>Multiplicación</strong> base 4 de dos operados de 4 bits. . . . . . . . . . . 46<br />

3.8. Codificación de los dígitos, alternativa (-X). . . . . . . . . . . . . 47<br />

3.9. <strong>Multiplicación</strong> base 4, alternativa (-X). . . . . . . . . . . . . . . . 48<br />

3.10. Estimación de consumo de recursos de un SMB4(3X). . . . . . . . 49<br />

3.11. Estimación de consumo de recursos lógicos SMB4(-X). . . . . . . 50<br />

3.12. Estimación de consumo de recursos lógicos de un SMSR. . . . . . 57<br />

3.13. Estimación de consumo de recursos lógicos SMF(SM). . . . . . . . 63<br />

3.14. Estimación de consumo de recursos lógicos de un SMF(SMSR). . 64<br />

viii

3.15. Ejemplo de una multiplicación mediante sumas consecutivas . . . 68<br />

3.16. Estimación de consumo de recursos lógicos de un SMSC(SM). . . 69<br />

3.17. Estimación de consumo de recursos lógicos de un SMSC(SMSR). . 70<br />

3.18. Estimación de consumo de recursos lógicos de la variante SMSR<br />

con redondeo a cero. . . . . . . . . . . . . . . . . . . . . . . . . . 84<br />

3.19. Estimación de consumo de recursos lógicos de la variante SMSR<br />

con redondeo a +∞. . . . . . . . . . . . . . . . . . . . . . . . . . 85<br />

3.20. Estimación de consumo de recursos lógicos de la variante SMSC<br />

con redondeo a cero. . . . . . . . . . . . . . . . . . . . . . . . . . 88<br />

3.21. Estimación de consumo de recursos lógicos de la variante SMSC<br />

con redondeo a +∞. . . . . . . . . . . . . . . . . . . . . . . . . . 90<br />

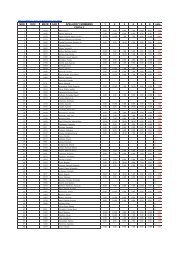

4.1. Consumo de recursos de los multiplicadores <strong>en</strong> Spartan[CLB]. . . 94<br />

4.2. Consumo Estimado de recursos de los multiplicadores [CLB]. . . . 94<br />

4.3. Difer<strong>en</strong>cia porc<strong>en</strong>tual, Consumo Experim<strong>en</strong>tal vs Estimado [ %]. . 95<br />

4.4. Consumo de recursos de los multiplicadores <strong>en</strong> Virtex [slices]. . . . 98<br />

4.5. Consumo de recursos de los multiplicadores <strong>en</strong> Virtex II [slices]. . 98<br />

4.6. Retardo de propagación de los multiplicadores <strong>en</strong> Spartan [ns]. . . 99<br />

4.7. Retardo estimado de propagación de los multiplicadores Trd = 0 [ns]. 99<br />

4.8. Difer<strong>en</strong>cia porc<strong>en</strong>tual, Retardo de propagación Experim<strong>en</strong>tal vs<br />

Estimado [ %]. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100<br />

4.9. Velocidad de Procesami<strong>en</strong>to de los multiplicadores <strong>en</strong> Spartan [Mops/s].100<br />

4.10. Velocidad de Procesami<strong>en</strong>to de los multiplicadores <strong>en</strong> Virtex [Mops/s].101<br />

4.11. Velocidad de Procesami<strong>en</strong>to de los multiplicadores <strong>en</strong> Virtex II<br />

[Mops/s]. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101<br />

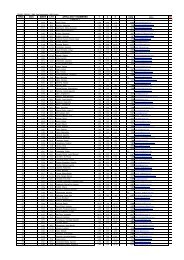

4.12. Consumo de recursos lógicos de los multiplicadores <strong>en</strong> punto flo-<br />

tante <strong>en</strong> Spartan [CLBs]. . . . . . . . . . . . . . . . . . . . . . . . 114<br />

ix

4.13. Consumo de recursos lógicos de las variantes <strong>en</strong> Virtex [slices]. . . 115<br />

4.14. Consumo de recursos lógicos de las variantes <strong>en</strong> Virtex II [slices]. . 115<br />

4.15. Comportami<strong>en</strong>to temporal de las variantes <strong>en</strong> Spartan [Mflop/s]. . 115<br />

4.16. Comportami<strong>en</strong>to temporal de las variantes <strong>en</strong> Virtex [Mflop/s]. . 116<br />

4.17. Comportami<strong>en</strong>to temporal de las variantes <strong>en</strong> Virtex II [Mflop/s]. 116<br />

5.1. Implem<strong>en</strong>tación de Multiplicadores Paralelos <strong>en</strong> FPGA. . . . . . . 122<br />

5.2. Resultados experim<strong>en</strong>tales de Multiplicadores <strong>Secu<strong>en</strong>cial</strong>es . . . . 123<br />

5.3. Resultados experim<strong>en</strong>tales de los Multiplicadores <strong>Secu<strong>en</strong>cial</strong>es pro-<br />

puestos. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124<br />

5.4. Resultados experim<strong>en</strong>tales de Multiplicadores <strong>en</strong> Punto Flotante . 125<br />

B.1. Punto flotante estándar. . . . . . . . . . . . . . . . . . . . . . . . 156<br />

B.2. Punto flotante a medida. . . . . . . . . . . . . . . . . . . . . . . . 157<br />

x

Índice de figuras<br />

2.1. Diagrama <strong>en</strong> bloques de un multiplicador <strong>en</strong> punto flotante . . . . 9<br />

2.2. Semisumador a) Símbolo lógico, b) y c) arquitectura. . . . . . . . 13<br />

2.3. Sumador total,a) símbolo lógico b) y c) arquitecturas. . . . . . . . 15<br />

2.4. Símbolo lógico de un CPA e implem<strong>en</strong>tación de un RCA. . . . . 16<br />

2.5. CSA a) Símbolo lógico y b) implem<strong>en</strong>tación con FAs. . . . . . . . 17<br />

2.6. Sumadores concat<strong>en</strong>ados a) con CPA, b) con CSA. . . . . . . . . 18<br />

2.7.<br />

Árbol de sumadores para m=9. . . . . . . . . . . . . . . . . . . . 19<br />

2.8. Multiplicador por Tabla de Look-up. . . . . . . . . . . . . . . . . 20<br />

2.9. Multiplicador Ripple Carry de 4 bits. . . . . . . . . . . . . . . . . 20<br />

2.10. PE de un multiplicador Ripple Carry. . . . . . . . . . . . . . . . . 21<br />

2.11. Esquema de un multiplicador Ripple Carry mediante PEs. . . . . 21<br />

2.12. Multiplicador Carry Save de 4 bits. . . . . . . . . . . . . . . . . . 22<br />

2.13. PE de un multiplicador Carry Save. . . . . . . . . . . . . . . . . . 22<br />

2.14. Esquema de un multiplicador Carry Save mediante PEs. . . . . . 23<br />

2.15. PE de un multiplicador paralelo Guild. . . . . . . . . . . . . . . . 23<br />

2.16. Multiplicador paralelo Guild. . . . . . . . . . . . . . . . . . . . . . 24<br />

2.17. PE de un multiplicador Mccanny - Mcwhinter. . . . . . . . . . . . 25<br />

2.18. Multiplicador paralelo Mccanny - Mcwhinter. . . . . . . . . . . . 26<br />

2.19. Consumo de recursos lógicos de MP. . . . . . . . . . . . . . . . . 28<br />

2.20. Multiplicadores proporcionados por Xilinx. . . . . . . . . . . . . . 29<br />

xi

2.21. Implem<strong>en</strong>tación de Multiplicadores n = 8 . . . . . . . . . . . . . . 30<br />

2.22. Implem<strong>en</strong>tación de Multiplicadores n = 16 . . . . . . . . . . . . . 30<br />

2.23. Implem<strong>en</strong>tación de un multiplicador optimizado <strong>en</strong> área de Xilinx<br />

n = 32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31<br />

3.1. Multiplicador SM con desplazami<strong>en</strong>to a la derecha. . . . . . . . . 37<br />

3.2. Multiplicador SM con desplazami<strong>en</strong>to a la derecha con registro<br />

compartido. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38<br />

3.3. Multiplicador SM con desplazami<strong>en</strong>to a la izquierda. . . . . . . . 39<br />

3.4. Consumo de recursos del SM. . . . . . . . . . . . . . . . . . . . . 41<br />

3.5. Esquema de retardos <strong>en</strong> un sumador. . . . . . . . . . . . . . . . . 42<br />

3.6. Retardo de propagación estimado del SM. . . . . . . . . . . . . . 44<br />

3.7. Máxima frecu<strong>en</strong>cia de reloj estimada aplicable al SM. . . . . . . . 44<br />

3.8. Velocidad máxima de procesami<strong>en</strong>to del SM. . . . . . . . . . . . . 45<br />

3.9. Diagrama de un SMB4(3X). . . . . . . . . . . . . . . . . . . . . . 47<br />

3.10. Diagrama de un SMB4(-X). . . . . . . . . . . . . . . . . . . . . . 49<br />

3.11. Diagrama de la variante del SMB4(-X). . . . . . . . . . . . . . . . 50<br />

3.12. Consumo de recursos de multiplicadores SM. . . . . . . . . . . . . 52<br />

3.13. Retardo de propagación estimado del SMB4(3X). . . . . . . . . . 53<br />

3.14. Máxima frecu<strong>en</strong>cia de reloj estimada aplicable al SMB4(3X). . . . 53<br />

3.15. Velocidad máxima de procesami<strong>en</strong>to del SMB4(3X). . . . . . . . . 54<br />

3.16. Retardo de propagación estimado del SMB4(-X). . . . . . . . . . 55<br />

3.17. Máxima frecu<strong>en</strong>cia de reloj estimada aplicable al SMB4(-X). . . . 55<br />

3.18. Velocidad máxima de procesami<strong>en</strong>to del SMB4(-X). . . . . . . . . 56<br />

3.19. Multiplicador SMSR. . . . . . . . . . . . . . . . . . . . . . . . . . 57<br />

3.20. Consumo de recursos del SMSR. . . . . . . . . . . . . . . . . . . . 58<br />

3.21. Retardo de propagación estimado del SMSR. . . . . . . . . . . . . 59<br />

xii

3.22. Máxima frecu<strong>en</strong>cia de reloj estimada aplicable al SMSR. . . . . . 60<br />

3.23. Velocidad máxima de procesami<strong>en</strong>to del SMSR. . . . . . . . . . . 60<br />

3.24. Diagrama de operación de un SMF. . . . . . . . . . . . . . . . . . 62<br />

3.25. Consumo de recursos de multiplicadores SMF. . . . . . . . . . . . 65<br />

3.26. Retardo de propagación estimado del SMF. . . . . . . . . . . . . . 66<br />

3.27. Máxima frecu<strong>en</strong>cia de reloj estimada aplicable al SMF. . . . . . . 66<br />

3.28. Velocidad máxima de procesami<strong>en</strong>to de los SMF. . . . . . . . . . 67<br />

3.29. Ejemplo de un SMSC(SM). . . . . . . . . . . . . . . . . . . . . . 68<br />

3.30. Ejemplo de un SMSC(SMSR). . . . . . . . . . . . . . . . . . . . . 69<br />

3.31. Consumo de recursos estimado de un SMSC. . . . . . . . . . . . . 71<br />

3.32. Ruta crítica de dos sumas consecutivas. . . . . . . . . . . . . . . . 72<br />

3.33. Retardo de propagación estimado del SMSC. . . . . . . . . . . . . 73<br />

3.34. Máxima frecu<strong>en</strong>cia de reloj estimada aplicable al SMSC. . . . . . 74<br />

3.35. Velocidad máxima de procesami<strong>en</strong>to del SMSC. . . . . . . . . . . 74<br />

3.36. Consumo de recursos lógicos de un SM vs SMSR. . . . . . . . . . 75<br />

3.37. Velocidad de procesami<strong>en</strong>to de un SM vs SMSR. . . . . . . . . . . 76<br />

3.38. Consumo de recursos lógicos de los multiplicadores optimizados <strong>en</strong><br />

velocidad. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77<br />

3.39. Velocidad de procesami<strong>en</strong>to de los multiplicadores optimizados <strong>en</strong><br />

velocidad. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78<br />

3.40. Índice de performance de los multiplicadores. . . . . . . . . . . . . 79<br />

3.41. Índice de performance de los multiplicadores 20 < n < 32. . . . . 80<br />

3.42. Modificación del SMSR para el producto de las mantisas . . . . . 81<br />

3.43. Ejemplo del esquema de redondeo implem<strong>en</strong>tado . . . . . . . . . . 83<br />

3.44. <strong>Multiplicación</strong> de las mantisas. . . . . . . . . . . . . . . . . . . . . 83<br />

3.45. Consumo de recursos del PFPM(SMSR), r = 8. . . . . . . . . . . 85<br />

3.46. Consumo de recursos del PFPM(SMSR), r = 8. . . . . . . . . . . 86<br />

xiii

3.47. SMSC modificado para el producto de las mantisas . . . . . . . . 87<br />

3.48. Consumo de recursos del PFPM(SMSC), r = 8. . . . . . . . . . . 89<br />

3.49. Consumo de recursos del PFPM(SMSC), r = 8. . . . . . . . . . . 91<br />

4.1. Síntesis de un CLB del multiplicador SM. . . . . . . . . . . . . . . 95<br />

4.2. Consumo de recursos lógicos del SM <strong>en</strong> Spartan. . . . . . . . . . . 96<br />

4.3. Consumo de recursos lógicos del SM <strong>en</strong> Spartan. . . . . . . . . . . 97<br />

4.4. Consumo de recursos lógicos: SM vs SMSR <strong>en</strong> Spartan. . . . . . . 102<br />

4.5. Consumo de recursos lógicos: SM vs SMSR <strong>en</strong> Virtex. . . . . . . . 103<br />

4.6. Consumo de recursos lógicos: SM vs SMSR <strong>en</strong> Virtex II. . . . . . 103<br />

4.7. Velocidad de procesami<strong>en</strong>to: SM vs SMSR <strong>en</strong> Spartan. . . . . . . 104<br />

4.8. Velocidad de procesami<strong>en</strong>to: SM vs SMSR <strong>en</strong> Virtex. . . . . . . . 104<br />

4.9. Velocidad de procesami<strong>en</strong>to: SM vs SMSR <strong>en</strong> Virtex II. . . . . . . 105<br />

4.10. Consumo de recursos lógicos de multiplicadores optimizados <strong>en</strong><br />

velocidad <strong>en</strong> Spartan. . . . . . . . . . . . . . . . . . . . . . . . . . 106<br />

4.11. Consumo de recursos lógicos de multiplicadores optimizados <strong>en</strong><br />

velocidad <strong>en</strong> Virtex. . . . . . . . . . . . . . . . . . . . . . . . . . . 106<br />

4.12. Consumo de recursos lógicos de multiplicadores optimizados <strong>en</strong><br />

velocidad <strong>en</strong> Virtex II. . . . . . . . . . . . . . . . . . . . . . . . . 107<br />

4.13. Velocidad de procesami<strong>en</strong>to de los multiplicadores optimizados <strong>en</strong><br />

velocidad <strong>en</strong> Spartan. . . . . . . . . . . . . . . . . . . . . . . . . . 108<br />

4.14. Velocidad de procesami<strong>en</strong>to de multiplicadores optimizados <strong>en</strong> ve-<br />

locidad <strong>en</strong> Virtex. . . . . . . . . . . . . . . . . . . . . . . . . . . . 108<br />

4.15. Velocidad de procesami<strong>en</strong>to de multiplicadores optimizados <strong>en</strong> ve-<br />

locidad <strong>en</strong> Virtex II. . . . . . . . . . . . . . . . . . . . . . . . . . 109<br />

4.16. Índice de performance de los multiplicadores <strong>en</strong> Spartan, 8 ≤ n ≤ 20.110<br />

xiv

4.17. Índice de performance de los multiplicadores <strong>en</strong> Spartan, 20 ≤ n ≤<br />

32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110<br />

4.18. Índice de performance de los multiplicadores <strong>en</strong> Virtex, 8 ≤ n ≤ 20. 111<br />

4.19. Índice de performance de los multiplicadores <strong>en</strong> Virtex, 20 ≤ n ≤ 32.112<br />

4.20. Índice de performance de los multiplicadores <strong>en</strong> Virtex II, 8 ≤ n ≤ 20.113<br />

4.21. Índice de performance de los multiplicadores <strong>en</strong> Virtex II, 20 ≤<br />

n ≤ 32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113<br />

4.22. Índice de performance de los multiplicadores con redondeo a cero<br />

<strong>en</strong> Spartan. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117<br />

4.23. Índice de performance de los multiplicadores con redondeo a +∞<br />

<strong>en</strong> Spartan. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118<br />

4.24. Índice de performance de los multiplicadores con redondeo a +∞<br />

<strong>en</strong> Virtex. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118<br />

4.25. Índice de performance de los multiplicadores con redondeo a +∞<br />

<strong>en</strong> Virtex II. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119<br />

A.1. Diagrama <strong>en</strong> bloques de un CPLD . . . . . . . . . . . . . . . . . . 140<br />

A.2. Distribución de bloques de una FPGA de Xilinx . . . . . . . . . . 141<br />

A.3. Matriz de interconexión de una FPGA de Xilinx . . . . . . . . . . 143<br />

A.4. Descripción de un LE de una FPGA FLEX10K de Altera . . . . . 144<br />

A.5. Descripción de un CLB de una FPGA XC4000 de Xilinx . . . . . 145<br />

A.6. Recursos lógicos de algunas FPGAs de Xilinx . . . . . . . . . . . 146<br />

A.7. Lógica de acarreo dedicada de una FPGA XC4000 de Xilinx . . . 148<br />

B.1. Esquema de formatos numéricos . . . . . . . . . . . . . . . . . . . 151<br />

C.1. Esquema de motores de una sección del CLIC. . . . . . . . . . . . 161<br />

xv

C.2. Sistema de control de movimi<strong>en</strong>to de motores de accionami<strong>en</strong>to<br />

increm<strong>en</strong>tal. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162<br />

C.3. Diagrama de flujo de un algoritmo on-line. . . . . . . . . . . . . . 163<br />

C.4. Perfil de velocidad trapezoidal. . . . . . . . . . . . . . . . . . . . . 164<br />

C.5. Perfil de velocidad, deseado, cuantizado y la temporización resul-<br />

tante. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166<br />

C.6. (Izquierda) Posición y velocidad con el algoritmo iterativo. (Dere-<br />

cha) Detalle del perfil de posición y velocidad del perfil iterativo . 167<br />

C.7. Arquitectura hardware del algoritmo de g<strong>en</strong>eración de perfil de<br />

velocidad. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168<br />

C.8. Implem<strong>en</strong>tación del multiplicador Ripple Carry <strong>en</strong> una FPGA XC4006E.170<br />

C.9. Implem<strong>en</strong>tación de un multiplicador optimizado <strong>en</strong> área de Xilinx<br />

<strong>en</strong> una FPGA XC4006E. . . . . . . . . . . . . . . . . . . . . . . . 171<br />

C.10.Perfil de velocidad y posición del accionami<strong>en</strong>to controlado por un<br />

sistema basado <strong>en</strong> FPGA. 15 rev<br />

s<br />

≡ 6000 pasos<br />

s . . . . . . . . . . . . 173<br />

C.11.Perfil de velocidad del accionami<strong>en</strong>to controlado por un sistema<br />

basado <strong>en</strong> FPGA. 62,5 rev<br />

s<br />

≡ 25000 pasos<br />

s . . . . . . . . . . . . . . . 174<br />

C.12.Perfil de velocidad del accionami<strong>en</strong>to utilizando el modo de micro-<br />

pasos. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176<br />

C.13.Perfiles de posición y velocidad para un sistema de accionami<strong>en</strong>to<br />

<strong>en</strong> modomicropaso. . . . . . . . . . . . . . . . . . . . . . . . . . . 177<br />

xvi

Agradecimi<strong>en</strong>tos<br />

A Mario<br />

A Daniel<br />

A mis colegas <strong>en</strong> el Laboratorio de Instrum<strong>en</strong>tación y Control<br />

xvii

Resum<strong>en</strong><br />

El objetivo principal de esta tesis fue desarrollar arquitecturas de multiplicado-<br />

res binarios de m<strong>en</strong>or consumo de recursos lógicos que las exist<strong>en</strong>tes, mant<strong>en</strong>i<strong>en</strong>do<br />

las prestaciones de velocidad de cálculo. El propósito particular fue implem<strong>en</strong>tar<br />

las mismas <strong>en</strong> los dispositivos digitales d<strong>en</strong>ominados FPGA (Field Programmable<br />

Gate Array).<br />

Para ello se investigaron las estructuras de multiplicación del tipo secu<strong>en</strong>cial<br />

que se caracterizan por poseer un consumo de recursos reducido y una velocidad<br />

de procesami<strong>en</strong>to baja.<br />

Se modelizaron los multiplicadores a partir del desarrollo de ecuaciones que<br />

permit<strong>en</strong> estimar el consumo de recursos lógicos y el desempeño temporal de los<br />

mismos. Se desarrollaron nuevas arquitecturas que se compararon con las exis-<br />

t<strong>en</strong>tes. Se introdujo un nuevo indicador d<strong>en</strong>ominado índice de performance, que<br />

permite cuantificar el costo de un multiplicador para una dada FPGA. Los resul-<br />

tados teóricos se corroboraron con un exhaustivo trabajo experim<strong>en</strong>tal mediante<br />

el cual se han validado las ecuaciones obt<strong>en</strong>idas.<br />

A partir de la validación de los modelos de los multiplicadores, se determina-<br />

ron los esquemas de mayor desempeño que cumpl<strong>en</strong> con los objetivos deseados.<br />

Así se arribó a multiplicadores <strong>en</strong> punto fijo con los que se obtuvo un consu-<br />

mo de recursos hasta 8 veces m<strong>en</strong>or y una velocidad comparable a la de una<br />

arquitectura exist<strong>en</strong>te. Los avances se ext<strong>en</strong>dieron a la multiplicación <strong>en</strong> punto<br />

xviii

flotante, obt<strong>en</strong>i<strong>en</strong>dose esquemas de bajo consumo de recursos y bu<strong>en</strong>a velocidad<br />

de procesami<strong>en</strong>to.<br />

xix

Nom<strong>en</strong>clatura<br />

1C Complem<strong>en</strong>to a 1<br />

2C Complem<strong>en</strong>to a 2<br />

ALP Arreglo Lógico Programable<br />

ASIC Application Specific Integrated Circuit<br />

CLB Configurable Logic Block<br />

CPA Carry Propagate Adder<br />

CPLD Complex Programmable Logic Device<br />

CSA Carry Save Adder<br />

DSP Digital Signal Processor<br />

FA Full Adder<br />

FF Flip Flop<br />

FG Function G<strong>en</strong>erator<br />

FPGA Field Programmable Gate Array<br />

GAL G<strong>en</strong>eric Array Logic<br />

HA Half Adder<br />

LSB Least Significant Bit<br />

LUT Look-up Table<br />

xx

MAC Multiplicador/Acumulador<br />

MP Multiplicador Paralelo<br />

PAL Programmable Array Logic<br />

PE Procesador Elem<strong>en</strong>tal<br />

PLD Programmable Logic Device<br />

PROM Programmable Read Only Memory<br />

PS Processing Speed<br />

RCA Ripple Carry Adder<br />

SM Multiplicador <strong>Secu<strong>en</strong>cial</strong><br />

SMB4 Multiplicador <strong>Secu<strong>en</strong>cial</strong> de base 4<br />

SMF Multiplicador <strong>Secu<strong>en</strong>cial</strong> Fraccionado<br />

SMSC Multiplicador <strong>Secu<strong>en</strong>cial</strong> de Sumas Consecutivas<br />

SMSR Multiplicador <strong>Secu<strong>en</strong>cial</strong> Sin <strong>en</strong>tradas Registradas<br />

SR Shift Register<br />

VHDL Very high speed integrated circuit Hardware Description Lan-<br />

fc<br />

pi<br />

guage<br />

Máxima frecu<strong>en</strong>cia de reloj<br />

Bit i del operando P<br />

P Operando Producto<br />

TBY P<br />

Tc<br />

TCK<br />

TCKO<br />

CIN to COUT bypass delay<br />

Tiempo de cálculo<br />

Período de reloj<br />

Clock-to-output delay<br />

xxi

TILO<br />

TOCP Y<br />

tpd<br />

Trd<br />

TSUM<br />

F/G inputs to X/Y outputs delay<br />

Operand inputs (F1, F2, G1, G4) to COUT delay<br />

Propagation delay<br />

Route delay<br />

CIN through function g<strong>en</strong>erator to X/Y output delay<br />

X, Y Operando Multiplicando y multiplicador respectivam<strong>en</strong>te<br />

xi, yi<br />

Vmin<br />

Vmax<br />

Bit i del operando Multiplicando y Multiplicador respectivam<strong>en</strong>-<br />

te<br />

Velocidad mínima<br />

Velocidad máxima<br />

Vr(k) Velocidad de refer<strong>en</strong>cia para el paso k-esimo<br />

∆t(k) Período de tiempo <strong>en</strong>tre el paso actual y el próximo<br />

xxii

Capítulo 1<br />

Introducción<br />

En el Procesami<strong>en</strong>to Digital de Señales (PDS) se recurre, como operación<br />

elem<strong>en</strong>tal, al producto de dos operandos y la posterior adición de un tercero,<br />

estructura conocida como MAC (Multiplicador/Acumulador).<br />

Los dispositivos de cálculo más empleados <strong>en</strong> el PDS son los DSPs (Digital<br />

Signal Processors). Si bi<strong>en</strong> los DSPs son baratos y flexibles, pose<strong>en</strong> sólo una uni-<br />

dad MAC por lo que un proceso aritmético demanda la ejecución secu<strong>en</strong>cial de las<br />

operaciones. Como consecu<strong>en</strong>cia, una operación algorítmica consume un deter-<br />

minado tiempo de ejecución y, si fuera necesario utilizar un tiempo de ejecución<br />

m<strong>en</strong>or, conv<strong>en</strong>dría adoptar hardware a medida, alternativa proporcionada por los<br />

ASICs (Application-Specific Integrated Circuit) y las FPGAs (Field Programma-<br />

ble Gate Array). Tanto los ASICs como las FPGAs posibilitan la utilización de<br />

varias MACs <strong>en</strong> paralelo, logrando de este modo una notable reducción del tiempo<br />

de procesami<strong>en</strong>to. Los ASICs admit<strong>en</strong> implem<strong>en</strong>tar sistemas complejos y resguar-<br />

dan la propiedad intelectual de los procesos debido a que no son copiables. Sin<br />

embargo implican un gran costo de fabricación por lo que no aceptan errores<br />

<strong>en</strong> su desarrollo y, consecu<strong>en</strong>tem<strong>en</strong>te, su utilización repres<strong>en</strong>ta un gran riesgo de<br />

producción.<br />

1

Capítulo 1. Introducción 2<br />

En cuanto a las FPGAs, éstas combinan la flexibilidad de un DSP con la<br />

velocidad y la d<strong>en</strong>sidad de compon<strong>en</strong>tes de un ASIC. Las FPGAs pose<strong>en</strong> una<br />

gran cantidad de recursos lógicos, un bajo costo de desarrollo ya que son fáciles de<br />

depurar y, fundam<strong>en</strong>talm<strong>en</strong>te, permit<strong>en</strong> al diseñador corregir errores y actualizar<br />

el diseño. Estas v<strong>en</strong>tajas conviert<strong>en</strong> a las FPGAs <strong>en</strong> dispositivos apropiados como<br />

procesadores de señales o aceleradores de cálculo.<br />

1.1. Estructuras de Multiplicadores<br />

Los multiplicadores se pued<strong>en</strong> clasificar según el modo <strong>en</strong> que ingresan los<br />

operandos [1] [2]. Si ambos operandos ingresan <strong>en</strong> forma serie se d<strong>en</strong>ominan<br />

serie/serie. La mayor v<strong>en</strong>taja de estos multiplicadores reside <strong>en</strong> el bajo núme-<br />

ro de <strong>en</strong>tradas/salidas utilizadas y <strong>en</strong> la bajo consumo de recursos lógicos, sin<br />

embargo estos multiplicadores se <strong>en</strong>cu<strong>en</strong>tran limitados a aplicaciones de baja<br />

velocidad [3] [4] [5]. Si sólo uno de los operandos ingresa <strong>en</strong> forma serie, el mul-<br />

tiplicador se d<strong>en</strong>omina serie/paralelo [6]. Este tipo de multiplicadores pres<strong>en</strong>tan<br />

un consumo de recursos lógicos moderado y son ideales para aplicaciones de velo-<br />

cidad media donde los multiplicadores serie/serie son demasiado l<strong>en</strong>tos. Si ambos<br />

operandos son ingresados <strong>en</strong> paralelo el tipo de multiplicador es d<strong>en</strong>ominado pa-<br />

ralelo/paralelo. Estos últimos son los que se tratarán <strong>en</strong> esta tesis debido a su<br />

capacidad de procesar los datos a alta velocidad.<br />

Los multiplicadores también se pued<strong>en</strong> clasificar <strong>en</strong> función del algoritmo de<br />

cálculo <strong>en</strong>: suma y desplazami<strong>en</strong>to, por árbol o contadores. Los multiplicadores<br />

por suma y desplazami<strong>en</strong>to utilizan el método conocido comúnm<strong>en</strong>te como lápiz<br />

y papel para calcular el producto. En algunos casos esta tarea se realiza constru-<br />

y<strong>en</strong>do una celda de procesami<strong>en</strong>to básica que se repite <strong>en</strong> un arreglo determinado.

Capítulo 1. Introducción 3<br />

La difer<strong>en</strong>cia de procesami<strong>en</strong>to de estos multiplicadores radica <strong>en</strong> el tipo de co-<br />

municación <strong>en</strong>tre estas celdas, que puede ser local (solo existe comunicación <strong>en</strong>tre<br />

celdas vecinas) o global (existe comunicación mas allá de la celda vecina). Con el<br />

objetivo de acelerar los productos parciales 1 C. Wallace [7] propuso originalm<strong>en</strong>te<br />

una estructura de sumadores, conocida como Árbol de Wallace, donde el retardo<br />

de la suma es proporcional el logaritmo del número de sumandos. Otro modo de<br />

acelerar los productos parciales consiste <strong>en</strong> la utilización de contadores parale-<br />

los [8] para obt<strong>en</strong>er la suma de los bits que forman las columnas de la matriz de<br />

productos parciales.<br />

Los multiplicadores que realizan el algoritmo de suma y desplazami<strong>en</strong>to <strong>en</strong><br />

forma simultánea son d<strong>en</strong>ominados habitualm<strong>en</strong>te multiplicadores paralelos. Es-<br />

tos multiplicadores realizan el producto rápidam<strong>en</strong>te, pero son difíciles de realizar<br />

cuando un dispositivo posee una cantidad de recursos limitada. Este problema se<br />

ac<strong>en</strong>túa, cuando el formato de los operandos esta expresado <strong>en</strong> punto flotante.<br />

Los multiplicadores <strong>en</strong> punto flotante utilizan típicam<strong>en</strong>te multiplicadores para-<br />

lelos para el producto de las mantisas [9] [10]. A medida que se increm<strong>en</strong>ta la<br />

complejidad de la operación, el consumo de recursos lógicos utilizados aum<strong>en</strong>ta<br />

notablem<strong>en</strong>te y consecu<strong>en</strong>tem<strong>en</strong>te los costos de implem<strong>en</strong>tación.<br />

Un esquema de multiplicación de operandos <strong>en</strong> paralelo que utiliza una m<strong>en</strong>or<br />

cantidad de recursos lógicos es el d<strong>en</strong>ominado Shift and Add [11] [12] o secu<strong>en</strong>cial<br />

(SM). Esta reducción del consumo de recursos se realiza a costa de ejecutar tantas<br />

iteraciones como longitud de palabra posean los operandos [13] [14]. Esto repre-<br />

s<strong>en</strong>ta una seria desv<strong>en</strong>taja debido al excesivo tiempo de cálculo y por esta razón<br />

han sido excluidos de las aplicaciones típicas. Por otro lado, si se puede mejorar<br />

el desempeño <strong>en</strong> velocidad sin incurrir <strong>en</strong> la cantidad de recursos que requiere un<br />

1 En la multiplicación de dos números <strong>en</strong>teros de n bits se d<strong>en</strong>omina producto parcial al<br />

producto un bit del multiplicador por el multiplicando.

Capítulo 1. Introducción 4<br />

multiplicador paralelo, estos multiplicadores pued<strong>en</strong> resultar más v<strong>en</strong>tajosos.<br />

1.2. Objetivos de la tesis<br />

El objetivo principal de esta tesis consiste <strong>en</strong> el desarrollo de multiplicado-<br />

res con un reducido consumo de recursos lógicos, que mant<strong>en</strong>gan un desempeño<br />

aceptable de la velocidad de procesami<strong>en</strong>to.<br />

En función de este objetivo, se caracterizarán las arquitecturas de los multi-<br />

plicadores exist<strong>en</strong>tes. Se propondrán variantes que incluyan la multiplicación de<br />

operandos <strong>en</strong> punto fijo y punto flotante.<br />

1.3. Organización de la tesis<br />

Esta tesis está dividida <strong>en</strong> cinco capítulos. El Capítulo 1 pres<strong>en</strong>ta el estado<br />

del arte e introduce aspectos de la temática de esta tesis. El Capítulo 2 pres<strong>en</strong>ta<br />

conceptos básicos sobre la multiplicación. Se pres<strong>en</strong>tan los esquemas de Multi-<br />

plicadores Paralelos, los cuales se caracterizan y se <strong>en</strong>sayan con el objetivo de<br />

cuantificar la problemática de consumo de recursos.<br />

El Capítulo 3 está dedicado al desarrollo de la propuesta que consiste <strong>en</strong> la<br />

aplicación de Multiplicadores <strong>Secu<strong>en</strong>cial</strong>es al producto binario <strong>en</strong> punto fijo y <strong>en</strong><br />

punto flotante. En este capítulo se desarrollan difer<strong>en</strong>tes esquemas de Multipli-<br />

cación <strong>Secu<strong>en</strong>cial</strong> para los cuales se estima su desempeño <strong>en</strong> cuanto a la cantidad<br />

de recursos lógicos y velocidad de procesami<strong>en</strong>to.<br />

El Capítulo 4 está dedicado a la verificación experim<strong>en</strong>tal. Para ello se ex-<br />

plicita la implem<strong>en</strong>tación práctica de los difer<strong>en</strong>tes esquemas desarrollados sobre<br />

algunas familias de FPGAs. El objetivo de este capítulo es la contrastación de las<br />

estimaciones obt<strong>en</strong>idas <strong>en</strong> el capítulo anterior con los resultados experim<strong>en</strong>tales.

Capítulo 1. Introducción 5<br />

En el mismo se establec<strong>en</strong> criterios de comparación, <strong>en</strong> términos de performance,<br />

<strong>en</strong>tre los multiplicadores propuestos y otros exist<strong>en</strong>tes.<br />

Adicionalm<strong>en</strong>te, se pres<strong>en</strong>tan cuatro apéndices, a saber:<br />

El Apéndice A realiza una breve descripción de los <strong>Dispositivos</strong> <strong>Lógicos</strong> Pro-<br />

gramables y sus características.<br />

El Apéndice B introduce los formatos numéricos utilizados <strong>en</strong> PDS.<br />

El Apéndice C describe la aplicación específica de los multiplicadores secu<strong>en</strong>-<br />

ciales <strong>en</strong> el Procesami<strong>en</strong>to Digital utilizado <strong>en</strong> el área de Control de Movimi<strong>en</strong>to.<br />

En el mismo se aprovechan las prestaciones que brindan los multiplicadores <strong>en</strong> la<br />

implem<strong>en</strong>tación hardware de un algoritmo de control de posición.<br />

Finalm<strong>en</strong>te, el Apéndice D pres<strong>en</strong>ta los trabajos publicados como resultado<br />

del trabajo de tesis.

Capítulo 2<br />

Arquitecturas de Multiplicadores<br />

2.1. Introducción<br />

La utilización de FPGA <strong>en</strong> el Procesami<strong>en</strong>to Digital de Señales (PDS) es su-<br />

mam<strong>en</strong>te v<strong>en</strong>tajosa. Una de las v<strong>en</strong>tajas consiste <strong>en</strong> la posibilidad de lograr un<br />

hardware a medida que incluya desde la selección de la longitud de palabra de<br />

los operandos hasta la ejecución de los cálculos. Un hardware a medida puede<br />

realizar cálculos más rápidam<strong>en</strong>te que uno programable porque pued<strong>en</strong> disponer-<br />

se varias unidades de cálculo <strong>en</strong> una sola FPGA. Estos multiplicadores pued<strong>en</strong><br />

operar indep<strong>en</strong>di<strong>en</strong>tes de modo de explotar toda la pot<strong>en</strong>cial concurr<strong>en</strong>cia de un<br />

algoritmo. Adicionalm<strong>en</strong>te, <strong>en</strong> la FPGA se pued<strong>en</strong> ejecutar otros procesos, como<br />

at<strong>en</strong>ción de periféricos, comunicación, etc. sin interferir con el procesami<strong>en</strong>to.<br />

En PDS [15] [16] [17] los procesos recurr<strong>en</strong>, como operación elem<strong>en</strong>tal, al<br />

producto de dos operandos y la posterior adición de un tercero, d<strong>en</strong>ominada<br />

MAC (Multiplicador/Acumulador). En una MAC, la multiplicación demanda una<br />

mayor cantidad de recursos lógicos que la adición.<br />

En este capítulo se realiza un repaso de conceptos de la multiplicación de ope-<br />

randos <strong>en</strong> punto fijo y punto flotante. Luego, para compr<strong>en</strong>der las arquitecturas<br />

6

Capítulo 2. Arquitecturas de Multiplicadores 7<br />

de los multiplicadores se introduc<strong>en</strong> aspectos relativos a la adición. Finalm<strong>en</strong>te,<br />

se pres<strong>en</strong>tan las estructuras de multiplicadores paralelos y su implem<strong>en</strong>tación <strong>en</strong><br />

FPGA.<br />

2.2. Algoritmo de la <strong>Multiplicación</strong><br />

2.2.1. Operandos <strong>en</strong> punto fijo<br />

<strong>Multiplicación</strong> de <strong>en</strong>teros sin signo<br />

n−1 <br />

j=0<br />

El producto de dos operandos binarios de n bits, un multiplicando, X =<br />

xj2j y un multiplicador, Y = n−1 <br />

yj2j está repres<strong>en</strong>tado por la Ec. (2.1).<br />

j=0<br />

P = Y · X (2.1)<br />

n−1<br />

= yj2 j · X (2.2)<br />

j=0<br />

n−1<br />

= 2 j · yjX (2.3)<br />

j=0<br />

Este producto, para dos operadores binarios de 4 bits sin signo X e Y , se<br />

puede observar <strong>en</strong> la Tabla 2.1.<br />

Tabla 2.1: Producto de dos operandos de 4 bits<br />

x3 x2 x1 x0<br />

y3 y2 y1 y0<br />

s03 s02 s01 s00 ≡ y0X2 0<br />

s13 s12 s11 s10 ≡ y1X2 1<br />

+ s23 s22 s21 s20 ≡ y2X2 2<br />

s33 s32 s31 s30 ≡ y3X2 3<br />

p7 p6 p5 p4 p3 p2 p1 p0 ≡ P<br />

producto parcial S = sj,n−1, ..., sj,2, sj,1, sj,0 con j = 0, 1, 2 · n − 1<br />

Producto P = p2n−1, ..., p2, p1, p0

Capítulo 2. Arquitecturas de Multiplicadores 8<br />

El producto P se obti<strong>en</strong>e como la suma de todos los productos parciales cada<br />

uno desplazado 2 j veces a la izquierda con j = 0, ..., n − 1. Este producto es<br />

conocido también como método del lápiz y papel.<br />

<strong>Multiplicación</strong> de <strong>en</strong>teros con signo<br />

En sistemas de magnitud con signo, la magnitud y el signo son repres<strong>en</strong>tados<br />

<strong>en</strong> forma separada. Exist<strong>en</strong> multiples formatos para expresar los números con<br />

signo, como por ejemplo Magnitud y Signo, Complem<strong>en</strong>to a 1 (1C) y Comple-<br />

m<strong>en</strong>to a 2 (2C) (ver Sección B.2.1).<br />

La multiplicación de dos operandos expresados <strong>en</strong> Magnitud y Signo se efectúa<br />

como un producto de <strong>en</strong>teros sin signo, y se ejecuta con una función XOR para<br />

procesar el signo.<br />

El producto de dos operandos expresados <strong>en</strong> 1C o 2C se puede efectuar reali-<br />

zando el complem<strong>en</strong>to del operando negativo, multiplicando luego como <strong>en</strong>teros<br />

sin signo y, finalm<strong>en</strong>te, complem<strong>en</strong>tando el resultado si sólo uno de ellos hubiese<br />

estado complem<strong>en</strong>tado. Este tipo de multiplicación puede resultar s<strong>en</strong>cillo para<br />

el caso de 1C, pero repres<strong>en</strong>ta bastante complejidad para el caso de 2C. En este<br />

caso, se puede aplicar el método de lápiz y papel siempre que los operandos sean<br />

positivos o que el multiplicando sea negativo y el multiplicador positivo. En am-<br />

bos casos la suma acumulativa de los productos parciales arrojará un resultado<br />

correcto mi<strong>en</strong>tras que la acumulación contemple la ext<strong>en</strong>sión de signo. Esto es,<br />

si el bit más significativo es 0, se desplaza el operando introduci<strong>en</strong>do un 0. En el<br />

caso <strong>en</strong> que este bit sea 1, el desplazami<strong>en</strong>to se realiza introduci<strong>en</strong>do un 1.<br />

Cuando el multiplicador sea negativo se debe realizar una corrección al pro-<br />

cedimi<strong>en</strong>to m<strong>en</strong>cionado que consiste <strong>en</strong> restar el multiplicando <strong>en</strong> el último paso,<br />

<strong>en</strong> vez de adicionarlo.

Capítulo 2. Arquitecturas de Multiplicadores 9<br />

2.2.2. Operandos <strong>en</strong> punto flotante<br />

Los sistemas numéricos de punto flotante fueron desarrollados para operar<br />

con precisión sobre un gran rango dinámico. Sin embargo, este formato numérico<br />

requiere algoritmos aritméticos más complejos.<br />

La multiplicación de dos operandos <strong>en</strong> punto flotante incluye varias operacio-<br />

nes: obt<strong>en</strong>ción del signo, adición de los expon<strong>en</strong>tes, multiplicación de las mantisas<br />

y normalización del resultado (Ecs. (2.4 - 2.7)).<br />

C = A × B = SC · 2 eC−bias · 1.fC<br />

SC = SA ⊕ SB<br />

(2.4)<br />

(2.5)<br />

eC = eA + eB − bias (2.6)<br />

1.fC = 1.fA × 1.fB<br />

(2.7)<br />

El algoritmo para la multiplicación <strong>en</strong> punto flotante se repres<strong>en</strong>ta de manera<br />

sintética <strong>en</strong> la Fig. 2.1.<br />

Etapa 1<br />

Etapa 2<br />

Etapa 3<br />

Bits de signo Expon<strong>en</strong>tes Mantisas<br />

OR-exclusiva<br />

Adición de<br />

expon<strong>en</strong>tes<br />

Ajuste de<br />

bias<br />

Ajuste de<br />

expon<strong>en</strong>te<br />

Producto de<br />

mantisas<br />

Redondeo<br />

Normalización<br />

Bit de signo Ofl. Expon<strong>en</strong>te Mantisa<br />

Figura 2.1: Diagrama <strong>en</strong> bloques de un multiplicador <strong>en</strong> punto flotante

Capítulo 2. Arquitecturas de Multiplicadores 10<br />

ción:<br />

Las Ecs. (2.4 - 2.7) se realizan <strong>en</strong> varias etapas, que se describ<strong>en</strong> a continua-<br />

Etapa 1:<br />

Se adicionan los expon<strong>en</strong>tes eA y eB; si el resultado es m<strong>en</strong>or que la repre-<br />

s<strong>en</strong>tación, se produce un desbordami<strong>en</strong>to de capacidad inferior (underflow).<br />

En este caso el resultado de toda la operación se fija al valor ”cero”. En el<br />

caso de un overflow, el resultado se fija <strong>en</strong> el máximo número que el formato<br />

puede repres<strong>en</strong>tar.<br />

Si el operando C es distinto de cero, se concat<strong>en</strong>a el 1 implícito a la izquier-<br />

da del fraccional (fA y fB) repres<strong>en</strong>tado de cada operando y se realiza el<br />

producto <strong>en</strong>tero de los números binarios resultantes (Ec. (2.7)).<br />

Si el operando C es distinto de cero, se realiza la operación XOR de los<br />

signos de los operandos A y B.<br />

Etapa 2:<br />

Se ajusta el bias del expon<strong>en</strong>te. Este ajuste se debe a que cada uno de los<br />

expon<strong>en</strong>tes de los operandos posee un bias (ver Sección B.2.2) y la adición<br />

de dos operandos produce un desplazami<strong>en</strong>to superior al repres<strong>en</strong>tado por<br />

el formato.<br />

Sólo se almac<strong>en</strong>an los n bits más significativos del producto <strong>en</strong>tero de la<br />

etapa anterior de longitud 2n bits. Se realiza una operación de redondeo<br />

sobre la mantisa resultante.<br />

Etapa 3:<br />

Se normaliza el resultado de la mantisa dep<strong>en</strong>di<strong>en</strong>do del bit más significativo<br />

del producto de la Ec. (2.7).

Capítulo 2. Arquitecturas de Multiplicadores 11<br />

Se ajusta el expon<strong>en</strong>te dep<strong>en</strong>di<strong>en</strong>do de la normalización del producto de las<br />

mantisas.<br />

Redondeo<br />

Se conforma el signo, el expon<strong>en</strong>te y la mantisa <strong>en</strong> el formato repres<strong>en</strong>tado.<br />

La norma IEEE 754 [18], que trata el formato <strong>en</strong> punto flotante, especifican<br />

cuatro tipos de redondeo: redondeo al más cercano, redondeo a +∞, redondeo a<br />

−∞ y redondeo a cero.<br />

Redondeo al más cercano (al par <strong>en</strong> caso de empate): El estándar IEEE<br />

recomi<strong>en</strong>da este redondeo por defecto. En este caso se obti<strong>en</strong>e el valor re-<br />

pres<strong>en</strong>table más cercano al resultado infinitesimalm<strong>en</strong>te preciso.<br />

Redondeo a +∞: El estándar indica que el valor obt<strong>en</strong>ido debe ser el más<br />

cercano y no m<strong>en</strong>or que el resultado infinitesimalm<strong>en</strong>te preciso. Básicam<strong>en</strong>te<br />

esto significa que, para un resultado positivo, si los bits a la derecha del LSB<br />

son todos 0, <strong>en</strong>tonces el resultado es correcto. Si por el contrario, cualquiera<br />

de estos bits es 1, <strong>en</strong>tonces se debe adicionar un 1 al LSB.<br />

Redondeo a −∞: Este estándar indica que el valor obt<strong>en</strong>ido debe ser el más<br />

cercano y no mayor que el resultado infinitesimalm<strong>en</strong>te preciso. Básicam<strong>en</strong>te<br />

esto significa que, para un resultado negativo, si los bits a la derecha del LSB<br />

son todos 0, <strong>en</strong>tonces el resultado es correcto. Si por el contrario, cualquiera<br />

de estos bits es 1, <strong>en</strong>tonces se debe adicionar un 1 al LSB.<br />

Redondeo a cero: En el redondeo a cero el resultado es más cercano y<br />

no mayor <strong>en</strong> magnitud que el resultado infinitesimalm<strong>en</strong>te preciso. Este<br />

redondeo se aplica truncando el resultado a la derecha del LSB.

Capítulo 2. Arquitecturas de Multiplicadores 12<br />

Normalización<br />

Si el producto de mantisas de la Ec. (2.7) resulta <strong>en</strong> el rango 2 ≤ p ≤ 4,<br />

se debe realizar un desplazami<strong>en</strong>to de normalización a la derecha para restaurar<br />

el producto al rango 1 ≤ pr ≤ 2, con el apropiado ajuste del expon<strong>en</strong>te <strong>en</strong> una<br />

unidad.<br />

2.3. Adición<br />

2.3.1. Semisumador<br />

El Sumador Parcial (SP) también llamado Semisumador de un bit (Half Adder<br />

- HA) adiciona dos operandos de un bit y g<strong>en</strong>era como resultado un operando<br />

de dos bits. El bit m<strong>en</strong>os significativo es el bit suma, que surge de realizar la<br />

operacion de OR-EXC s = a ⊕ b. El bit más significativo resulta de realizar la<br />

operación AND, cout = ab. Este bit es llamado bit de acarreo de salida debido al<br />

desborde de la adición.<br />

La expresión aritmética de un sumador parcial se puede observar <strong>en</strong> las Ecs.<br />

(2.8,2.9 y 2.9), a partir de las que se despr<strong>en</strong>de el cálculo del bit s y el bit de<br />

acarreo.<br />

2 · cout + s = a + b (2.8)<br />

s = (a + b) mod 2<br />

cout = (a + b)div2 = 1<br />

(a + b − s) (2.9)<br />

2<br />

En la Fig. 2.2 se puede observar el símbolo lógico y dos posibles implem<strong>en</strong>ta-<br />

ciones del HA.

Capítulo 2. Arquitecturas de Multiplicadores 13<br />

c out<br />

ab<br />

HA<br />

s<br />

(a)<br />

c out<br />

Figura 2.2: Semisumador a) Símbolo lógico, b) y c) arquitectura.<br />

2.3.2. Sumador Total<br />

A difer<strong>en</strong>cia del HA, el sumador total (Full Adder - FA) posee una tercer<br />

<strong>en</strong>trada d<strong>en</strong>ominada bit de acarreo de <strong>en</strong>trada (cin). Esta <strong>en</strong>trada es utilizada<br />

para recibir una señal de acarreo de un bit m<strong>en</strong>os significativo.<br />

Las Ecs. (2.10 y 2.11) repres<strong>en</strong>tan las ecuaciones lógicas que gobiernan el<br />

funcionami<strong>en</strong>to del sumador.<br />

ab<br />

s<br />

(b)<br />

s = a ⊕ b ⊕ cin<br />

cout = ab + acin + bcin<br />

c out<br />

s<br />

(c)<br />

ab<br />

(2.10)<br />

(2.11)<br />

Las Ecs. (2.12 - 2.15) repres<strong>en</strong>tan las ecuaciones aritméticas correspondi<strong>en</strong>tes.<br />

2 · cout + s = a + b + cin<br />

(2.12)<br />

s = (a + b + cin) mod 2 (2.13)<br />

cout = (a + b + cin)div2 (2.14)<br />

= 1<br />

2 (a + b + cin − s) (2.15)<br />

Otra forma de describir el funcionami<strong>en</strong>to del FA consiste <strong>en</strong> declarar dos<br />

señales, una señal de g<strong>en</strong>eración (g) y una señal de propagación (p). La señal g

Capítulo 2. Arquitecturas de Multiplicadores 14<br />

indica cuando una señal de acarreo 0 o 1 es g<strong>en</strong>erada d<strong>en</strong>tro del sumador. La<br />

señal p indica cuando una señal de acarreo de <strong>en</strong>trada es propagada por el FA sin<br />

cambio hacia el acarreo de salida. Adicionalm<strong>en</strong>te se defin<strong>en</strong> para este sistema<br />

dos señales intermedias de acarreo, c 0 y c 1 , que pued<strong>en</strong> ser calculadas para el caso<br />

de cin = 0 y cin = 1. De esta manera, la salida de acarreo puede ser expresada<br />

mediante (g, p) o (c 0 , c 1 ) y la señal de acarreo de <strong>en</strong>trada puede ser realizada<br />

utilizando compuertas AND-OR o mediante una estructura de multiplexación.<br />

g = ab (2.16)<br />

p = a ⊕ b (2.17)<br />

c 0 = ab (2.18)<br />

c 1 = a + b (2.19)<br />

s = a ⊕ b ⊕ cin = p ⊕ cin<br />

cout = ab + acin + bcin<br />

= ab + (a + b)cin = ab + (a ⊕ b)cin<br />

= g + cin<br />

= ¯pg + pcin = ¯pa + pcin<br />

= ¯cinc 0 + cinc 1<br />

(2.20)<br />

(2.21)<br />

Se debe t<strong>en</strong>er <strong>en</strong> cu<strong>en</strong>ta que para el cálculo de cout utilizando una estructura<br />

AND-OR, la señal de propagación puede ser formulada como p = a + b pero para<br />

el cálculo del bit de la adición debe ser implem<strong>en</strong>tada como p = a ⊕ b.<br />

Un FA puede ser implem<strong>en</strong>tado a partir de dos sumadores parciales, compuer-<br />

tas de dos <strong>en</strong>tradas, multiplexores, o arreglos más complejos. En la Fig. 2.3 se<br />

pued<strong>en</strong> observar a), el símbolo del sumador, y dos alternativas de implem<strong>en</strong>tación:<br />

mediante dos semisumadores y mediante compuertas lógicas.

Capítulo 2. Arquitecturas de Multiplicadores 15<br />

Figura 2.3: Sumador total,a) símbolo lógico b) y c) arquitecturas.<br />

2.3.3. Suma por Propagación de Acarreo<br />

Una suma de propagación de acarreo (Carry Propagate Adder - CPA) adiciona<br />

dos operandos de n bits A = (an−1, an−2..., a0), B = (bn−1, bn−2..., b0) y una señal<br />

de acarreo de <strong>en</strong>trada opcional. El resultado está repres<strong>en</strong>tado por un operando<br />

de (n + 1) bits que consiste <strong>en</strong> un operando S = (sn−1, sn−2..., s0) de n bits y una<br />

señal de acarreo de salida.<br />

Las Ecs. (2.22 y 2.23) repres<strong>en</strong>tan las ecuaciones lógicas de cada sumador.<br />

Se puede notar que el acarreo de salida de un bit m<strong>en</strong>os significativo se propaga<br />

hacia un acarreo de <strong>en</strong>trada de un bit más significativo.<br />

sj = aj ⊕ bj ⊕ cj<br />

cj+1 = ajbj + (a ⊕ bj)cj<br />

Las Ecs. (2.24 - 2.27) repres<strong>en</strong>tan las ecuaciones aritméticas correspondi<strong>en</strong>tes.<br />

2 n · cout + S = A + B + cin<br />

(2.22)<br />

(2.23)<br />

(2.24)

Capítulo 2. Arquitecturas de Multiplicadores 16<br />

2 n n−1<br />

· cout +<br />

j=0<br />

<br />

2 j n−1<br />

sj = 2 j n−1<br />

aj + 2 j bj + cin<br />

j=0<br />

<br />

j=0<br />

n−1<br />

= 2 j (aj + bj) + cin<br />

j=0<br />

donde j = 0, 1, .., n − 1 y c0 = cin y cn = cout.<br />

(2.25)<br />

(2.26)<br />

2cj+1 + sj = (aj + bj + cj) (2.27)<br />

En la Fig. 2.4 se muestra el símbolo de este sumador, que puede ser im-<br />

plem<strong>en</strong>tado mediante varios FAs, y es comúnm<strong>en</strong>te d<strong>en</strong>ominado Ripple Carry<br />

Adder (RCA). Se observa que se g<strong>en</strong>era una propagación de la señal de acarreo<br />

c out<br />

A B<br />

CPA<br />

S<br />

(a)<br />

a n-1 b n-1<br />

cin cout FA<br />

s n-1<br />

...<br />

c n-1<br />

Figura 2.4: Símbolo lógico de un CPA e implem<strong>en</strong>tación de un RCA.<br />

que dep<strong>en</strong>de de la longitud de palabra de los operandos. La propagación de esta<br />

señal influye directam<strong>en</strong>te <strong>en</strong> la velocidad de procesami<strong>en</strong>to del sumador debido<br />

al retardo g<strong>en</strong>erado.<br />

2.3.4. Suma Carry-Save<br />

Una suma Carry-Save evita la propagación del acarreo ubicando a los acarreos<br />

intermedios como salidas <strong>en</strong> vez de colocarlos <strong>en</strong> la cad<strong>en</strong>a de propagación. La<br />

suma de dos operandos de n bits pres<strong>en</strong>ta dos dos palabras resultantes, S (suma),<br />

y C (acarreo). Este sumador acepta tres operandos binarios de <strong>en</strong>trada uno de<br />

los cuales podría operar como acarreo de <strong>en</strong>trada.<br />

c 2<br />

(b)<br />

a 1 b 1<br />

FA<br />

s 1<br />

c 1<br />

a 0 b 0<br />

FA<br />

s 0<br />

c in

Capítulo 2. Arquitecturas de Multiplicadores 17<br />

Las Ecs. (2.28, 2.29 y 2.30) repres<strong>en</strong>tan las ecuaciones aritméticas correspon-<br />

di<strong>en</strong>tes.<br />

dónde i = 0, 1, .., n − 1.<br />

n<br />

i=0<br />

2 i ci +<br />

2 · C + S = A0 + A1 + A2<br />

n−1<br />

2 n−1<br />

i=0<br />

2 i si =<br />

2ci+1 + si =<br />

j=0<br />

2<br />

j=0<br />

i=0<br />

aj,i<br />

2 i aj,i<br />

(2.28)<br />

(2.29)<br />

(2.30)<br />

El CSA se construye a partir de un arreglo lineal de FAs y posee un retardo<br />

constante indep<strong>en</strong>di<strong>en</strong>te de la longitud de palabra de los operandos, Fig. 2.5. Este<br />

a 2 a 1<br />

CSA<br />

c<br />

(a)<br />

s<br />

a 0<br />

c n<br />

a2,n-1a1,n-1 a0,n-1 FA<br />

s n-1<br />

...<br />

c 2<br />

a 2,1 a 1,1 a 0,1<br />

(b)<br />

FA<br />

s 1<br />

c 1<br />

a 2,0 a 1,0 a 0,0<br />

Figura 2.5: CSA a) Símbolo lógico y b) implem<strong>en</strong>tación con FAs.<br />

tipo de suma es utilizada <strong>en</strong> la g<strong>en</strong>eración de arreglos de sumadores e implica la<br />

necesidad de una suma final que aplique los acarreos correspondi<strong>en</strong>tes a la suma<br />

resultante.<br />

2.3.5. Suma Multi-operandos<br />

Una suma multi-operando es utilizada <strong>en</strong> la adición de m operandos de n<br />

bits, A0, ...., Am−1(m > 2) arrojando un resultado S con una repres<strong>en</strong>tación de<br />

(n + [log m]) bits.<br />

S =<br />

m−1 <br />

j=0<br />

Aj<br />

FA<br />

s 0<br />

(2.31)

Capítulo 2. Arquitecturas de Multiplicadores 18<br />

Un sumador multi-operando puede ser realizado mediante la concat<strong>en</strong>ación<br />

serie de m − 1 sumadores de Propagación de Acarreo (ó RCAs) ó de m − 2<br />

sumadores Carry-Save seguidos de un sumador de Propagación de Acarreo.<br />

Ambos tipos de sumadores concat<strong>en</strong>ados son similares <strong>en</strong> cuanto a su es-<br />

tructura lógica, y requerimi<strong>en</strong>tos de hardware, así como la longitud de camino<br />

crítico. La mayor difer<strong>en</strong>cia <strong>en</strong>tre ambas opciones es el arribo de los bits al último<br />

sumador de propagación.<br />

En el sumador implem<strong>en</strong>tado sólo con RCAs los bits más significativos arriban<br />

más tarde que los m<strong>en</strong>os significativos, debido a la propagación de la señal de<br />

acarreo. Por otro lado, <strong>en</strong> el sumador implem<strong>en</strong>tado con CSAs, el arribo de los<br />

bits es balanceado, dep<strong>en</strong>di<strong>en</strong>do la propagación del acarreo fundam<strong>en</strong>talm<strong>en</strong>te<br />

del CPA de la última etapa, que típicam<strong>en</strong>te es un RCA, Fig. 2.6.<br />

FA<br />

s n<br />

A 0<br />

CPA<br />

A 1<br />

CPA<br />

A 2<br />

CPA<br />

s n-1...0<br />

A 3<br />

A 0 A 1A 2<br />

CSA<br />

CSA<br />

CPA<br />

(a) (b)<br />

Figura 2.6: Sumadores concat<strong>en</strong>ados a) con CPA, b) con CSA.<br />

Otra suma multi-operando es la propuesta por Wallace [7] también d<strong>en</strong>omi-<br />

nada árbol de sumadores (o Wallace tree). Está compuesto de sumadores CSA <strong>en</strong><br />

un arreglo de árbol con un CPA final. Esta estructura esta diseñada para obt<strong>en</strong>er<br />

un retardo de propagación mínimo. La estructura de árbol posee tantas secciones<br />

como sean necesarias para reducir el número de sumandos a sólo dos. En la última<br />

S<br />

A 2<br />

A 3

Capítulo 2. Arquitecturas de Multiplicadores 19<br />

etapa, se utiliza un CPA rápido que ejecuta la adición del sumando y el acarreo<br />

final. En la Fig. 2.7 se muestra un árbol de sumadores para m = 9.<br />

A 0 A 1A 2<br />

CSA<br />

CSA<br />

A 3 A 4A 5<br />

CSA<br />

CSA<br />

CSA<br />

CSA<br />

CPA<br />

S<br />

A 6 A 7A 8<br />

CSA<br />

Figura 2.7: Árbol de sumadores para m=9.<br />

2.4. Multiplicadores Paralelos<br />

El multiplicador paralelo (MP) ejecuta el producto de dos operandos si-<br />

multáneam<strong>en</strong>te o <strong>en</strong> ”paralelo”. Exist<strong>en</strong> númerosos esquemas de MPs y las va-<br />

riantes radican <strong>en</strong> la forma <strong>en</strong> que se aborda la ejecución de los subproductos a<br />

fin de obt<strong>en</strong>er una mayor velocidad de procesami<strong>en</strong>to.<br />

2.4.1. Multiplicador por Tabla de Look-up<br />

El multiplicador por Tabla de Look-up no realiza cálculo, sino que opera como<br />

una memoria. Se concat<strong>en</strong>an los operandos X e Y constituy<strong>en</strong>do una dirección<br />

de memoria, Fig. 2.8, cuyo cont<strong>en</strong>ido es el valor del producto X · Y previam<strong>en</strong>te<br />

almac<strong>en</strong>ado. Si bi<strong>en</strong> este tipo de multiplicador dep<strong>en</strong>de de la velocidad de acceso<br />

a la memoria, es el más veloz que existe. Su desv<strong>en</strong>taja radica <strong>en</strong> la cantidad de

Capítulo 2. Arquitecturas de Multiplicadores 20<br />

recursos lógicos que demanda. A modo de ejemplo, un multiplicador de 16 bits<br />

requiere una memoria de 4,294,967,296x32 bits.<br />

XY<br />

DIR<br />

VALOR<br />

Figura 2.8: Multiplicador por Tabla de Look-up.<br />

2.4.2. Multiplicador Ripple Carry<br />

El multiplicador paralelo más difundido se basa <strong>en</strong> un esquema de propagación<br />

del acarreo tal como con la suma multi-operandos mediante CPA. Este multipli-<br />

cador es conocido como Multiplicador Ripple Carry. En la Fig. 2.9 se muestra un<br />

ejemplo de este producto para dos operandos de 4 bits.<br />

y 0<br />

y 1<br />

y 2<br />

y 3<br />

p 7<br />

FA<br />

FA<br />

FA<br />

FA<br />

FA<br />

x 3 x 3 x 1 x 0<br />

x 3 x 3 x 1 x 0<br />

x 3 x 3 x 1 x 0<br />

x 3 x 3 x 1 x 0<br />

FA<br />

p 6<br />

FA<br />

p 5<br />

FA<br />

p 4<br />

0<br />

Figura 2.9: Multiplicador Ripple Carry de 4 bits.<br />

FA<br />

p 3<br />

0<br />

FA<br />

FA<br />

p 2<br />

0<br />

P<br />

FA<br />

p 1<br />

0<br />

p 0

Capítulo 2. Arquitecturas de Multiplicadores 21<br />

Una forma de analizar un esquema de MP es a través de la síntesis de una uni-<br />

dad d<strong>en</strong>ominada PE (Procesador Elem<strong>en</strong>tal) que conti<strong>en</strong>e una compuerta AND y<br />

un FA, Fig. 2.10. Cada PE toma un bit de cada operando vía las <strong>en</strong>tradas ai y bi,<br />

calcula su producto a través de la compuerta AND, suma el resultado prov<strong>en</strong>i<strong>en</strong>te<br />

de un PE previo a través de si y el acarreo g<strong>en</strong>erado de un PE previo a través<br />

de ci. El resultado de la suma a la salida es so con el correspondi<strong>en</strong>te acarreo co.<br />

Los operandos son pasados a la salida a través de ao y bo.<br />

a o<br />

c o<br />

b o<br />

s i<br />

s o<br />

FA<br />

Figura 2.10: PE de un multiplicador Ripple Carry.<br />

El esquema del Multiplicador Ripple Carry repres<strong>en</strong>tado a partir de los PEs<br />

se puede observar <strong>en</strong> la Fig. 2.11.<br />

FA<br />

FA<br />

FA FA<br />

FA<br />

FA<br />

FA<br />

b i<br />

a i<br />

c i<br />

FA FA<br />

FA<br />

FA<br />

FA FA<br />

x 3 x 2 x 1 x 0<br />

FA FA<br />

p7 p6 p5 p4 p3 p2 p1 p0 Figura 2.11: Esquema de un multiplicador Ripple Carry mediante PEs.<br />

FA<br />

y 0<br />

y 1<br />

y 2<br />

y 3

Capítulo 2. Arquitecturas de Multiplicadores 22<br />

2.4.3. Multiplicador Carry Save<br />

Otro tipo de MP es el g<strong>en</strong>erado a partir de un esquema de propagación del<br />

acarreo como la suma Carry Save, Fig. 2.12. Este esquema busca romper la pro-<br />

pagación de la cad<strong>en</strong>a de acarreo para disminuir el retardo de cada suma, lo cual<br />

permite acelerar la multiplicación.<br />

p 7<br />

y 0<br />

y 1<br />

y 2<br />

y 3<br />

FA<br />

p 6<br />

FA<br />

FA<br />

HA<br />

FA<br />

x 3 x 3 x 1 x 0<br />

x 3 x3 x 1 x 0<br />

x 3 x 3 x 1 x 0<br />

x 3 x 3 x 1 x 0<br />

FA<br />

p 5<br />

0<br />

FA<br />

FA<br />

p 4<br />

Figura 2.12: Multiplicador Carry Save de 4 bits.<br />

FA<br />

Las Figs. 2.13 y 2.14 muestran el PE del multiplicador con propagación tipo<br />

Carry Save y el multiplicador mediante esta repres<strong>en</strong>tación.<br />

a o<br />

b o<br />

c o<br />

s i<br />

FA<br />

s o<br />

Figura 2.13: PE de un multiplicador Carry Save.<br />

p 3<br />

b i<br />

c i<br />

a i<br />

HA<br />

FA<br />

p 2<br />

HA<br />

p 1<br />

p 0

Capítulo 2. Arquitecturas de Multiplicadores 23<br />

FA<br />

FA<br />

FA<br />

FA<br />

FA<br />

FA<br />

FA<br />

FA<br />

FA<br />

FA<br />

FA<br />

FA<br />

FA<br />

FA<br />

x 3 x 2 x 1 x 0<br />

p7 p6 p5 p4 p3 p2 p1 p0 Figura 2.14: Esquema de un multiplicador Carry Save mediante PEs.<br />

2.4.4. Multiplicador Guild<br />

El MP propuesto por H. Guild [19] se muestra <strong>en</strong> la Fig. 2.16, cuyo PE es el<br />

de la Fig. 2.15.<br />

s i<br />

a o<br />

c o<br />

b i<br />

FA<br />

b o<br />

Figura 2.15: PE de un multiplicador paralelo Guild.<br />

Este multiplicador está estructurado <strong>en</strong> cad<strong>en</strong>as de sumadores para cada bit<br />

del producto, las cuales se <strong>en</strong>cu<strong>en</strong>tran <strong>en</strong> dirección diagonal desde la esquina<br />

izquierda superior a la derecha inferior. Cada sumador de la cad<strong>en</strong>a recibe un<br />

acarreo de <strong>en</strong>trada correspondi<strong>en</strong>te a una suma de la cad<strong>en</strong>a previa y <strong>en</strong>vía su<br />

c i<br />

a i<br />

s o<br />

FA<br />

FA<br />

FA<br />

FA<br />

FA<br />

FA<br />

y 0<br />

y 1<br />

y 2<br />

y 3

Capítulo 2. Arquitecturas de Multiplicadores 24<br />

salida de acarreo a un sumador de una cad<strong>en</strong>a posterior. El multiplicador Guild<br />

se caracteriza por una alta tasa de procesami<strong>en</strong>to, debido a la utilización de<br />

paralelismo y la posibilidad de implem<strong>en</strong>tación pipelines 1 .<br />

y 3 x 3 y 2 x 2 y 1 x 1 y 0 x 0<br />

FA<br />

FA<br />

FA<br />

FA FA<br />

FA<br />

FA FA<br />

FA FA<br />

FA<br />

FA<br />

FA<br />

p7 p6 p5 p4 p3 p2 p1 p0 Figura 2.16: Multiplicador paralelo Guild.<br />

1 Es una técnica de aceleración de procesos que se basa <strong>en</strong> la introducción latches o registros <strong>en</strong><br />

una apropiada posición del arreglo para separar la operación <strong>en</strong> etapas. Una vez implem<strong>en</strong>tada,<br />

el sistema increm<strong>en</strong>ta su velocidad de procesami<strong>en</strong>to como etapas posea.<br />

FA<br />

FA<br />

FA

Capítulo 2. Arquitecturas de Multiplicadores 25<br />

2.4.5. Multipicador McCanny-McWhinter<br />

Otro esquema de multiplicación paralelo es el propuesto por J. McCanny<br />

y J. McWhinter [20], Figs. 2.17 y 2.18. En la Fig. 2.18 se puede observar que<br />

el multiplicador esta estructurado <strong>en</strong> cad<strong>en</strong>as de sumadores para cada bit del<br />

producto, las cuales se <strong>en</strong>cu<strong>en</strong>tran <strong>en</strong> dirección vertical. Cada sumador de la<br />

cad<strong>en</strong>a recibe <strong>en</strong> forma diagonal un acarreo de <strong>en</strong>trada correspondi<strong>en</strong>te a una<br />

suma de la cad<strong>en</strong>a previa y <strong>en</strong>vía su salida de acarreo a un sumador de una<br />

cad<strong>en</strong>a posterior. Este multiplicador se caracteriza por pres<strong>en</strong>tar comunicación<br />

local <strong>en</strong>tre las celdas básicas.<br />

b o<br />