BLOCKING READER: DESIGN AND IMPLEMENTATION OF A ...

BLOCKING READER: DESIGN AND IMPLEMENTATION OF A ...

BLOCKING READER: DESIGN AND IMPLEMENTATION OF A ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

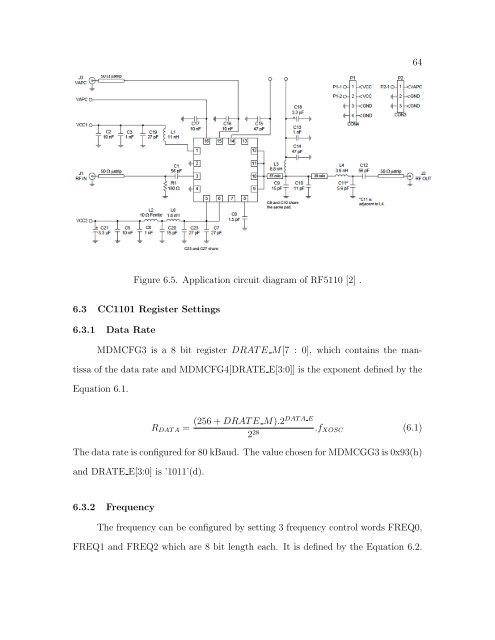

Figure 6.5. Application circuit diagram of RF5110 [2] .<br />

6.3 CC1101 Register Settings<br />

6.3.1 Data Rate<br />

MDMCFG3 is a 8 bit register DRAT E M[7 : 0], which contains the man-<br />

tissa of the data rate and MDMCFG4[DRATE E[3:0]] is the exponent defined by the<br />

Equation 6.1.<br />

RDAT A =<br />

(256 + DRAT E M).2DAT A E<br />

64<br />

2 28 .fXOSC (6.1)<br />

The data rate is configured for 80 kBaud. The value chosen for MDMCGG3 is 0x93(h)<br />

and DRATE E[3:0] is ’1011’(d).<br />

6.3.2 Frequency<br />

The frequency can be configured by setting 3 frequency control words FREQ0,<br />

FREQ1 and FREQ2 which are 8 bit length each. It is defined by the Equation 6.2.