Request

Request

Request

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

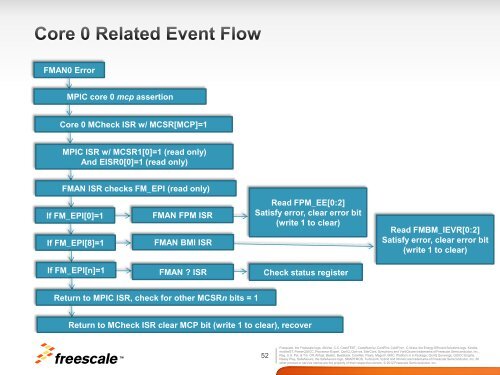

FMAN0 Error<br />

MPIC core 0 mcp assertion<br />

Core 0 MCheck ISR w/ MCSR[MCP]=1<br />

MPIC ISR w/ MCSR1[0]=1 (read only)<br />

And EISR0[0]=1 (read only)<br />

FMAN ISR checks FM_EPI (read only)<br />

If FM_EPI[0]=1 FMAN FPM ISR<br />

If FM_EPI[8]=1 FMAN BMI ISR<br />

If FM_EPI[n]=1<br />

TM<br />

FMAN ? ISR<br />

Return to MPIC ISR, check for other MCSRn bits = 1<br />

Read FPM_EE[0:2]<br />

Satisfy error, clear error bit<br />

(write 1 to clear)<br />

Check status register<br />

Return to MCheck ISR clear MCP bit (write 1 to clear), recover<br />

52<br />

Read FMBM_IEVR[0:2]<br />

Satisfy error, clear error bit<br />

(write 1 to clear)<br />

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis,<br />

mobileGT, PowerQUICC, Processor Expert, QorIQ, Qorivva, StarCore, Symphony and VortiQa are trademarks of Freescale Semiconductor, Inc.,<br />

Reg. U.S. Pat. & Tm. Off. Airfast, BeeKit, BeeStack, CoreNet, Flexis, MagniV, MXC, Platform in a Package, QorIQ Qonverge, QUICC Engine,<br />

Ready Play, SafeAssure, the SafeAssure logo, SMARTMOS, TurboLink, Vybrid and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All<br />

other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc.