Request

Request

Request

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

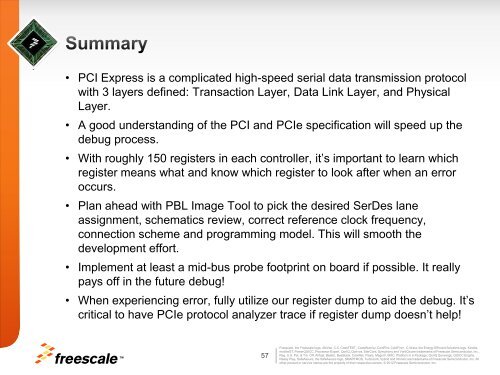

• PCI Express is a complicated high-speed serial data transmission protocol<br />

with 3 layers defined: Transaction Layer, Data Link Layer, and Physical<br />

Layer.<br />

• A good understanding of the PCI and PCIe specification will speed up the<br />

debug process.<br />

• With roughly 150 registers in each controller, it’s important to learn which<br />

register means what and know which register to look after when an error<br />

occurs.<br />

• Plan ahead with PBL Image Tool to pick the desired SerDes lane<br />

assignment, schematics review, correct reference clock frequency,<br />

connection scheme and programming model. This will smooth the<br />

development effort.<br />

• Implement at least a mid-bus probe footprint on board if possible. It really<br />

pays off in the future debug!<br />

• When experiencing error, fully utilize our register dump to aid the debug. It’s<br />

critical to have PCIe protocol analyzer trace if register dump doesn’t help!<br />

TM<br />

57<br />

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis,<br />

mobileGT, PowerQUICC, Processor Expert, QorIQ, Qorivva, StarCore, Symphony and VortiQa are trademarks of Freescale Semiconductor, Inc.,<br />

Reg. U.S. Pat. & Tm. Off. Airfast, BeeKit, BeeStack, CoreNet, Flexis, MagniV, MXC, Platform in a Package, QorIQ Qonverge, QUICC Engine,<br />

Ready Play, SafeAssure, the SafeAssure logo, SMARTMOS, TurboLink, Vybrid and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All<br />

other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc.