Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

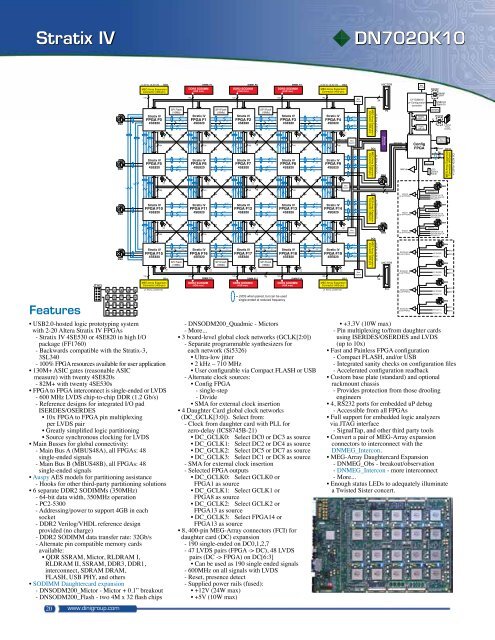

LED<br />

(x4)<br />

LED<br />

(x4)<br />

LED<br />

(x4)<br />

LED<br />

(x4)<br />

LED<br />

(x4)<br />

LED<br />

(x4)<br />

LED<br />

(x4)<br />

LED<br />

(x4)<br />

LED<br />

(x4)<br />

LED<br />

(x4)<br />

LED<br />

(x4)<br />

LED<br />

(x4)<br />

LED<br />

(x4)<br />

LED<br />

(x4)<br />

LED<br />

(x4)<br />

LED<br />

(x4)<br />

LED<br />

(x4)<br />

LED<br />

(x4)<br />

LED<br />

(x4)<br />

LED<br />

(x4)<br />

Config PROM<br />

Frequency<br />

Synths (Si5326)<br />

Frequency<br />

Synths (Si5326)<br />

Frequency<br />

Synths (Si5326)<br />

COMPACT FLASH<br />

<strong>FPGA</strong><br />

CONFIGURATION<br />

Stratix IV<br />

DN7020K10<br />

+1.5V to +3.3V I/O<br />

DC0<br />

MEG Array Expansion<br />

Connector (400-pin)<br />

DIMM_F1<br />

DDR2 SODIMM<br />

(4GB max)<br />

DIMM_F2<br />

DDR2 SODIMM<br />

(4GB max)<br />

DIMM_F3<br />

DDR2 SODIMM<br />

(4GB max)<br />

+1.5V to +3.3V I/O<br />

DC2<br />

MEG Array Expansion<br />

Connector (400-pin)<br />

MICTOR<br />

Boot<br />

EPROM<br />

RS232<br />

serial<br />

port<br />

SMA<br />

SMA<br />

SMA<br />

SMA<br />

12<br />

12<br />

12<br />

62 24 61<br />

190 120 120 120 190<br />

SPI Flash<br />

SPI Flash<br />

SPI Flash<br />

(16Mb)<br />

(16Mb)<br />

(16Mb)<br />

Stratix IV<br />

50 Stratix IV<br />

51 Stratix IV<br />

50 Stratix IV<br />

50 Stratix IV<br />

<strong>FPGA</strong> F0 <strong>FPGA</strong> F1 <strong>FPGA</strong> F2 <strong>FPGA</strong> F3 <strong>FPGA</strong> F4<br />

50<br />

4SE820<br />

4SE820<br />

62 24 61<br />

62 24 61<br />

62 24 61<br />

184<br />

188<br />

186<br />

48<br />

48<br />

48<br />

48<br />

48<br />

48<br />

46 50<br />

44 51<br />

46 50<br />

46<br />

4SE820<br />

4SE820<br />

4SE820<br />

50<br />

51<br />

50<br />

50<br />

51<br />

50<br />

48<br />

48<br />

48<br />

48<br />

48<br />

48<br />

138<br />

140<br />

138<br />

48<br />

48<br />

48<br />

48<br />

48<br />

48<br />

48<br />

48<br />

Stratix IV<br />

Stratix IV<br />

Stratix IV<br />

Stratix IV<br />

Stratix IV<br />

38<br />

39<br />

38<br />

38<br />

<strong>FPGA</strong> F5 <strong>FPGA</strong> F6 <strong>FPGA</strong> F7 <strong>FPGA</strong> F8 <strong>FPGA</strong> F9<br />

38<br />

39<br />

38<br />

38<br />

4SE820<br />

4SE820<br />

4SE820<br />

4SE820<br />

4SE820<br />

38<br />

48<br />

48<br />

Stratix IV<br />

Stratix IV<br />

Stratix IV<br />

Stratix IV<br />

Stratix IV<br />

<strong>FPGA</strong> F10<br />

38<br />

<strong>FPGA</strong> F11<br />

39<br />

<strong>FPGA</strong> F12<br />

38<br />

<strong>FPGA</strong> F13<br />

37<br />

<strong>FPGA</strong> F14<br />

38<br />

39<br />

38<br />

36<br />

4SE820<br />

4SE820<br />

4SE820<br />

4SE820<br />

4SE820<br />

38<br />

48<br />

48<br />

Stratix IV<br />

50 Stratix IV<br />

50<br />

<strong>FPGA</strong> F15 <strong>FPGA</strong> F16 <strong>FPGA</strong> F17 <strong>FPGA</strong> F18 <strong>FPGA</strong> F19<br />

4SE820<br />

4SE820<br />

40 50<br />

40 40 46<br />

Stratix IV<br />

51 Stratix IV<br />

51 Stratix IV<br />

51<br />

51<br />

51<br />

51 4SE820<br />

51 4SE820<br />

51 4SE820<br />

SPI Flash<br />

(16Mb)<br />

38<br />

38<br />

50<br />

24 23 24<br />

24 23 24<br />

24 23 24<br />

24 23 24<br />

39<br />

39<br />

SPI Flash<br />

(16Mb)<br />

39<br />

39<br />

51<br />

24 23 24<br />

24 23 24<br />

24 23 24<br />

24 23 24<br />

138<br />

140<br />

138<br />

48<br />

48<br />

48<br />

48<br />

48<br />

48<br />

48<br />

48<br />

48<br />

38<br />

38<br />

48<br />

48<br />

48<br />

48<br />

48<br />

48<br />

SPI Flash<br />

(16Mb)<br />

38<br />

38<br />

51<br />

24 23 24<br />

24 23 24<br />

24 23 24<br />

24 23 24<br />

140<br />

140<br />

138<br />

48<br />

48<br />

48<br />

48<br />

48<br />

48<br />

50<br />

50<br />

38<br />

36<br />

50<br />

48<br />

48<br />

38<br />

48<br />

48<br />

37<br />

48<br />

48<br />

50<br />

21 21 21<br />

21 21 21<br />

21 21 21<br />

21 21 21<br />

MBUS48B<br />

180<br />

184<br />

180<br />

Bus<br />

Switch<br />

47<br />

47<br />

48<br />

48<br />

Bus<br />

Switch<br />

47<br />

47<br />

48<br />

48<br />

Bus<br />

Switch<br />

47<br />

47<br />

48<br />

48<br />

47<br />

47<br />

48<br />

48<br />

Bus<br />

Switch<br />

DC3<br />

MEG Array Expansion<br />

Connector (400-pin)<br />

DC4<br />

MEG Array Expansion<br />

Connector (400-pin)<br />

DC5<br />

MEG Array Expansion<br />

Connector (400-pin)<br />

DC6<br />

MEG Array Expansion<br />

Connector (400-pin)<br />

+1.5V to +3.3V I/O +1.5V to +3.3V I/O +1.5V to +3.3V I/O +1.5V to +3.3V I/O<br />

34<br />

Main Bus<br />

Connector<br />

SMA<br />

SMA<br />

F4<br />

40<br />

40<br />

MICTOR<br />

MBUS48A<br />

MBUS48B<br />

MBCLK<br />

GCLK0<br />

(to all <strong>FPGA</strong>’s)<br />

GCLK1<br />

(to all <strong>FPGA</strong>’s)<br />

GCLK2<br />

(to all <strong>FPGA</strong>’s)<br />

DCGCLK0<br />

(to all <strong>FPGA</strong>’s)<br />

CY7C68013<br />

uP Configuration<br />

controller<br />

SRAM<br />

128Kb x 8<br />

Flash<br />

1 M x 8<br />

Config<br />

<strong>FPGA</strong><br />

48 MHz<br />

8<br />

LCD<br />

Control<br />

Panel<br />

USB 2.0<br />

(type b)<br />

RS232<br />

Reset<br />

96<br />

96<br />

SMA<br />

C<strong>FPGA</strong> Div Clk<br />

C<strong>FPGA</strong> Step Clk<br />

<strong>FPGA</strong> F19<br />

SMA<br />

C<strong>FPGA</strong> Div Clk<br />

C<strong>FPGA</strong> Step Clk<br />

<strong>FPGA</strong> F19<br />

SMA<br />

C<strong>FPGA</strong> Div Clk<br />

C<strong>FPGA</strong> Step Clk<br />

<strong>FPGA</strong> F19<br />

G0 Si5326<br />

<strong>FPGA</strong> F1<br />

4 Serial<br />

Ports<br />

(Tx/Rx)<br />

MEG Array Expansion<br />

Connector (400-pin)<br />

SMA<br />

PLL<br />

DC10<br />

SMA<br />

DC0<br />

DC3<br />

+1.5V to +3.3V I/O<br />

Features<br />

20<br />

JTAG<br />

www.dinigroup.com<br />

0<br />

5<br />

1<br />

6<br />

2<br />

7<br />

10 11 12 13 14<br />

15<br />

16<br />

17<br />

3<br />

8<br />

18<br />

4<br />

9<br />

19<br />

190 120 120 48<br />

DC1<br />

DIMM F16<br />

DIMM F17<br />

MEG Array Expansion<br />

Connector (400-pin)<br />

+1.5V to +3.3V I/O<br />

• USB2.0-hosted logic prototyping system<br />

with 2-20 Altera Stratix IV <strong>FPGA</strong>s<br />

- Stratix IV 4SE530 or 4SE820 in high I/O<br />

package (FF1760)<br />

- Backwards compatible with the Stratix-3,<br />

3SL340<br />

- 100% <strong>FPGA</strong> resources available for user application<br />

• 130M+ ASIC gates (reasonable ASIC<br />

measure) with twenty 4SE820s<br />

- 82M+ with twenty 4SE530s<br />

• <strong>FPGA</strong> to <strong>FPGA</strong> interconnect is single-ended or LVDS<br />

- 600 MHz LVDS chip-to-chip DDR (1.2 Gb/s)<br />

- Reference designs for integrated I/O pad<br />

ISERDES/OSERDES<br />

• 10x <strong>FPGA</strong> to <strong>FPGA</strong> pin multiplexing<br />

per LVDS pair<br />

• Greatly simplified logic partitioning<br />

• Source synchronous clocking for LVDS<br />

• Main Busses for global connectivity:<br />

- Main Bus A (MBUS48A), all <strong>FPGA</strong>s: 48<br />

single-ended signals<br />

- Main Bus B (MBUS48B), all <strong>FPGA</strong>s: 48<br />

single-ended signals<br />

• Auspy AES models for partitioning assistance<br />

- Hooks for other third-party partitioning solutions<br />

• 6 separate DDR2 SODIMMs (350MHz)<br />

- 64-bit data width, 350MHz operation<br />

- PC2-5300<br />

- Addressing/power to support 4GB in each<br />

socket<br />

- DDR2 Verilog/VHDL reference design<br />

provided (no charge)<br />

- DDR2 SODIMM data transfer rate: 32Gb/s<br />

- Alternate pin compatible memory cards<br />

available:<br />

• QDR SSRAM, Mictor, RLDRAM I,<br />

RLDRAM II, SSRAM, DDR3, DDR1,<br />

interconnect, SDRAM DRAM,<br />

FLASH, USB PHY, and others<br />

• SODIMM Daughtercard expansion<br />

- DNSODM200_Mictor - Mictor + 0.1” breakout<br />

- DNSODM200_Flash - two 4M x 32 flash chips<br />

DDR2 SODIMM<br />

(4GB max)<br />

DDR2 SODIMM<br />

(4GB max)<br />

= LVDS when paired, but can be used<br />

single-ended at reduced frequency<br />

120 190<br />

DIMM F18<br />

DDR2 SODIMM<br />

(4GB max)<br />

- DNSODM200_Quadmic - Mictors<br />

- More...<br />

• 3 board-level global clock networks (GCLK[2:0])<br />

- Separate programmable synthesizers for<br />

each network (Si5326)<br />

• Ultra-low jitter<br />

• 2 kHz – 710 MHz<br />

• User configurable via Compact FLASH or USB<br />

- Alternate clock sources:<br />

• Config <strong>FPGA</strong><br />

- single-step<br />

- Divide<br />

• SMA for external clock insertion<br />

• 4 Daughter Card global clock networks<br />

(DC_GCLK[3:0]). Select from:<br />

- Clock from daughter card with PLL for<br />

zero-delay (ICS8745B-21)<br />

• DC_GCLK0: Select DC0 or DC3 as source<br />

• DC_GCLK1: Select DC2 or DC4 as source<br />

• DC_GCLK2: Select DC5 or DC7 as source<br />

• DC_GCLK3: Select DC1 or DC8 as source<br />

- SMA for external clock insertion<br />

- Selected <strong>FPGA</strong> outputs<br />

• DC_GCLK0: Select GCLK0 or<br />

<strong>FPGA</strong>1 as source<br />

• DC_GCLK1: Select GCLK1 or<br />

<strong>FPGA</strong>8 as source<br />

• DC_GCLK2: Select GCLK2 or<br />

<strong>FPGA</strong>13 as source<br />

• DC_GCLK3: Select <strong>FPGA</strong>14 or<br />

<strong>FPGA</strong>13 as source<br />

• 8, 400-pin MEG-Array connectors (FCI) for<br />

daughter card (DC) expansion<br />

- 190 single-ended on DC0,1,2,7<br />

- 47 LVDS pairs (<strong>FPGA</strong> -> DC), 48 LVDS<br />

pairs (DC -> <strong>FPGA</strong>) on DC[6:3]<br />

• Can be used as 190 single ended signals<br />

- 600MHz on all signals with LVDS<br />

- Reset, presence detect<br />

- Supplied power rails (fused):<br />

• +12V (24W max)<br />

• +5V (10W max)<br />

MEG Array Expansion<br />

Connector (400-pin)<br />

+1.5V to +3.3V I/O<br />

DC7<br />

Bus<br />

Switch<br />

34<br />

F19<br />

DCGCLK1<br />

(to all <strong>FPGA</strong>’s)<br />

DCGCLK2<br />

(to all <strong>FPGA</strong>’s)<br />

DCGCLK3<br />

(to all <strong>FPGA</strong>’s)<br />

G1 Si5326<br />

<strong>FPGA</strong> F8<br />

G2 Si5326<br />

<strong>FPGA</strong> F13<br />

<strong>FPGA</strong> F13<br />

<strong>FPGA</strong> F14<br />

• +3.3V (10W max)<br />

- Pin multiplexing to/from daughter cards<br />

using ISERDES/OSERDES and LVDS<br />

(up to 10x)<br />

• Fast and Painless <strong>FPGA</strong> configuration<br />

- Compact FLASH, and/or USB<br />

- Integrated sanity checks on configuration files<br />

- Accelerated configuration readback<br />

• Custom base plate (standard) and optional<br />

rackmount chassis<br />

- Provides protection from those drooling<br />

engineers<br />

• 4, RS232 ports for embedded uP debug<br />

- Accessible from all <strong>FPGA</strong>s<br />

• Full support for embedded logic analyzers<br />

via JTAG interface<br />

- SignalTap, and other third party tools<br />

• Convert a pair of MEG-Array expansion<br />

connectors to interconnect with the<br />

DNMEG_Intercon.<br />

• MEG-Array Daughtercard Expansion<br />

- DNMEG_Obs - breakout/observation<br />

- DNMEG_Intercon - more interconnect<br />

- More...<br />

• Enough status LEDs to adequately illuminate<br />

a Twisted Sister concert.<br />

PLL<br />

SMA<br />

PLL<br />

SMA<br />

PLL<br />

DC2<br />

DC4<br />

DC5<br />

DC7<br />

DC1<br />

DC6