You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

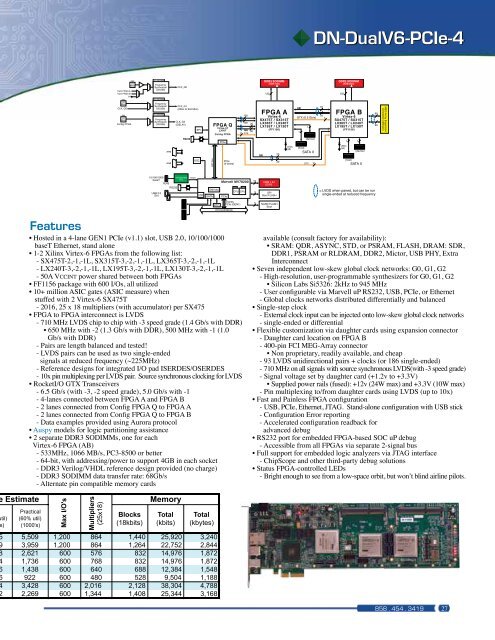

DN-DualV6-PCIe-4<br />

from <strong>FPGA</strong> A<br />

from <strong>FPGA</strong> B<br />

TP<br />

osc<br />

24<br />

MHz<br />

CLK_G0<br />

osc<br />

24<br />

MHz<br />

Config <strong>FPGA</strong><br />

osc<br />

24<br />

MHz<br />

114.285 MHz<br />

Frequency<br />

Synthesizer<br />

(Si5326)<br />

114.285 MHz<br />

Frequency<br />

Synthesizer<br />

(Si5326)<br />

114.285 MHz<br />

Frequency<br />

Synthesizer<br />

(Si5326)<br />

CLK_G0<br />

CLK_G1<br />

(2KHz to 945 MHz)<br />

CLK_G2<br />

(iDELAY)<br />

SPI<br />

<strong>FPGA</strong> Q<br />

Virtex-5T<br />

LX50T<br />

Config <strong>FPGA</strong><br />

100<br />

100 20<br />

QA 20<br />

2 GTX<br />

DDR3 SODIMM<br />

(4GB max)<br />

122<br />

<strong>FPGA</strong> A<br />

Virtex-6<br />

SX475T / SX315T<br />

LX365T / LX240T<br />

LX195T / LX130T<br />

(FF1156)<br />

AB<br />

GTX (6.5 Gb/s)<br />

1<br />

1<br />

79<br />

79<br />

4<br />

DDR3 SODIMM<br />

(4GB max)<br />

122<br />

<strong>FPGA</strong> B<br />

Virtex-6<br />

SX475T / SX315T<br />

LX365T / LX240T<br />

LX195T / LX130T<br />

(FF1156)<br />

99<br />

99<br />

MEG Array Expansion<br />

Connector (400-pin)<br />

RS232<br />

(device)<br />

PCIe<br />

LEDs<br />

(x8)<br />

(host)<br />

A<br />

JTAG<br />

SATA II<br />

B<br />

QB<br />

20<br />

OSC<br />

PCIe<br />

20<br />

JTAG Q<br />

(4-lanes)<br />

GTX 2<br />

MPP Bus<br />

1 1<br />

LEDs<br />

(x8)<br />

(device)<br />

(host)<br />

SATA II<br />

10/100/1000<br />

baseT<br />

RJ45<br />

USB 2.0<br />

(2x)<br />

RS232<br />

10/100/1000<br />

Phy<br />

RGMII<br />

USB<br />

DMA(4x)<br />

SATA<br />

Marvell MV78200<br />

PCIe<br />

FPU FPU<br />

CPU CPU<br />

64<br />

3<br />

128M x 64<br />

DDR2<br />

SPI<br />

Boot FLASH<br />

= LVDS when paired, but can be run<br />

single-ended at reduced frequency<br />

RTC<br />

4-lanes<br />

PCIe (GEN1)<br />

8<br />

NAND FLASH<br />

Boot<br />

PCI EXPRESS<br />

Features<br />

• Hosted in a 4-lane GEN1 PCIe (v1.1) slot, USB 2.0, 10/100/1000<br />

baseT Ethernet, stand alone<br />

• 1-2 Xilinx Virtex-6 <strong>FPGA</strong>s from the following list:<br />

- SX475T-2,-1,-1L, SX315T-3,-2,-1,-1L, LX365T-3,-2,-1,-1L<br />

- LX240T-3,-2,-1,-1L, LX195T-3,-2,-1,-1L, LX130T-3,-2,-1,-1L<br />

- 50A VCCINT power shared between both <strong>FPGA</strong>s<br />

• FF1156 package with 600 I/Os, all utilized<br />

• 10+ million ASIC gates (ASIC measure) when<br />

stuffed with 2 Virtex-6 SX475T<br />

- 2016, 25 x 18 multipliers (with accumulator) per SX475<br />

• <strong>FPGA</strong> to <strong>FPGA</strong> interconnect is LVDS<br />

- 710 MHz LVDS chip to chip with -3 speed grade (1.4 Gb/s with DDR)<br />

• 650 MHz with -2 (1.3 Gb/s with DDR), 500 MHz with -1 (1.0<br />

Gb/s with DDR)<br />

- Pairs are length balanced and tested!<br />

- LVDS pairs can be used as two single-ended<br />

signals at reduced frequency (~225MHz)<br />

- Reference designs for integrated I/O pad ISERDES/OSERDES<br />

- 10x pin multiplexing per LVDS pair. Source synchronous clocking for LVDS<br />

• RocketI/O GTX Transceivers<br />

- 6.5 Gb/s (with -3, -2 speed grade), 5.0 Gb/s with -1<br />

- 4-lanes connected between <strong>FPGA</strong> A and <strong>FPGA</strong> B<br />

- 2 lanes connected from Config <strong>FPGA</strong> Q to <strong>FPGA</strong> A<br />

- 2 lanes connected from Config <strong>FPGA</strong> Q to <strong>FPGA</strong> B<br />

- Data examples provided using Aurora protocol<br />

• Auspy models for logic partitioning assistance<br />

• 2 separate DDR3 SODIMMs, one for each<br />

Virtex-6 <strong>FPGA</strong> (AB)<br />

- 533MHz, 1066 MB/s, PC3-8500 or better<br />

- 64-bit, with addressing/power to support 4GB in each socket<br />

- DDR3 Verilog/VHDL reference design provided (no charge)<br />

- DDR3 SODIMM data transfer rate: 68Gb/s<br />

- Alternate pin compatible memory cards<br />

available (consult factory for availability):<br />

• SRAM: QDR, ASYNC, STD, or PSRAM, FLASH, DRAM: SDR,<br />

DDR1, PSRAM or RLDRAM, DDR2, Mictor, USB PHY, Extra<br />

Interconnect<br />

• Seven independent low-skew global clock networks: G0, G1, G2<br />

- High-resolution, user-programmable synthesizers for G0, G1, G2<br />

• Silicon Labs Si5326: 2kHz to 945 MHz<br />

- User configurable via Marvell uP RS232, USB, PCIe, or Ethernet<br />

- Global clocks networks distributed differentially and balanced<br />

• Single-step clock<br />

- External clock input can be injected onto low-skew global clock networks<br />

- single-ended or differential<br />

• Flexible customization via daughter cards using expansion connector<br />

- Daughter card location on <strong>FPGA</strong> B<br />

- 400-pin FCI MEG-Array connector<br />

• Non proprietary, readily available, and cheap<br />

- 93 LVDS unidirectional pairs + clocks (or 186 single-ended)<br />

- 710 MHz on all signals with source synchronous LVDS(with -3 speed grade)<br />

- Signal voltage set by daughter card (+1.2v to +3.3V)<br />

• Supplied power rails (fused): +12v (24W max) and +3.3V (10W max)<br />

- Pin multiplexing to/from daughter cards using LVDS (up to 10x)<br />

• Fast and Painless <strong>FPGA</strong> configuration<br />

- USB, PCIe, Ethernet, JTAG. Stand-alone configuration with USB stick<br />

- Configuration Error reporting<br />

- Accelerated configuration readback for<br />

advanced debug<br />

• RS232 port for embedded <strong>FPGA</strong>-based SOC uP debug<br />

- Accessible from all <strong>FPGA</strong>s via separate 2-signal bus<br />

• Full support for embedded logic analyzers via JTAG interface<br />

- ChipScope and other third-party debug solutions<br />

• Status <strong>FPGA</strong>-controlled LEDs<br />

- Bright enough to see from a low-space orbit, but won’t blind airline pilots.<br />

til)<br />

)<br />

Estimate<br />

Practical<br />

(60% util)<br />

(1000's)<br />

Max I/O's<br />

Multipliers<br />

(25x18)<br />

Blocks<br />

(18kbits)<br />

Memory<br />

Total<br />

(kbits)<br />

Total<br />

(kbytes)<br />

5,509 1,200 864 1,440 25,920 3,240<br />

3,959 1,200 864 1,264 22,752 2,844<br />

2,621 600 576 832 14,976 1,872<br />

1,736 600 768 832 14,976 1,872<br />

1,438 600 640 688 12,384 1,548<br />

922 600 480 528 9,504 1,188<br />

3,428 600 2,016 2,128 38,304 4,788<br />

2,269 600 1,344 1,408 25,344 3,168<br />

858 . 454 . 3419 27