Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

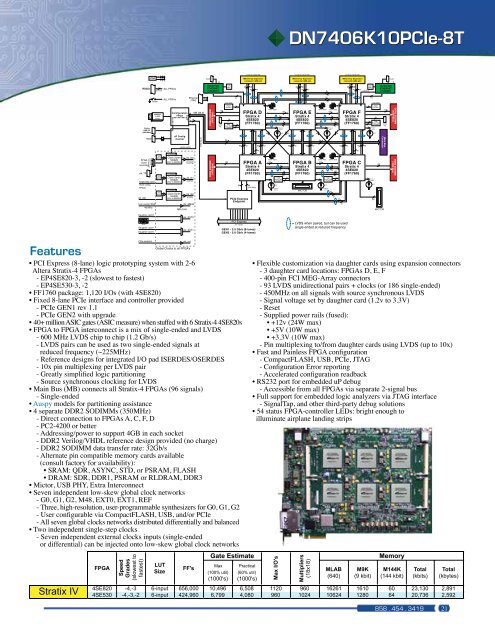

A<br />

B<br />

C<br />

D<br />

F<br />

A B C<br />

F<br />

E<br />

D<br />

F<br />

D<br />

<strong>FPGA</strong> A<br />

LED’s<br />

<strong>FPGA</strong> D<br />

LED’s<br />

18<br />

11<br />

<strong>FPGA</strong> B<br />

LED’s<br />

<strong>FPGA</strong> E<br />

LED<br />

<strong>FPGA</strong> F<br />

LED’s<br />

<strong>FPGA</strong> C<br />

LED’s<br />

DN7406K10PCIe-8T<br />

JTAG<br />

RJ45<br />

D<br />

+1.5V to +3.3V I/O<br />

MEG Array Expansion<br />

connector (400-pin)<br />

+1.5V to +3.3V I/O<br />

MEG Array Expansion<br />

connector (400-pin)<br />

+1.5V to +3.3V I/O<br />

MEG Array Expansion<br />

connector (400-pin)<br />

RJ45<br />

F<br />

RS232<br />

2<br />

(bussed)<br />

ALL <strong>FPGA</strong>s<br />

10/100/1000<br />

ETHERNET<br />

(VSC8601)<br />

125<br />

MHz<br />

48 48<br />

47 47<br />

48 48<br />

47 47<br />

9<br />

48 48<br />

47 47<br />

125<br />

MHz<br />

125 MHz<br />

10/100/1000<br />

ETHERNET<br />

(VSC8601)<br />

Config<br />

USB 2.0<br />

(480 Mb/s)<br />

RS232<br />

Reset<br />

COMPACT<br />

FLASH<br />

config<br />

ALL <strong>FPGA</strong>s<br />

Configuration<br />

<strong>FPGA</strong><br />

uP Config<br />

Control<br />

clock config<br />

Ethernet<br />

JTAG<br />

16<br />

MB [35:0]<br />

config data<br />

DDR2 SODIMM<br />

(4GB Max)<br />

QL5064<br />

122<br />

+2.5V<br />

I/O<br />

mac addr<br />

Flash<br />

(24C64)<br />

36<br />

8<br />

User<br />

Serial Flash<br />

(16 Mbit)<br />

1<br />

17<br />

2<br />

5<br />

<strong>FPGA</strong> D<br />

Stratix 4<br />

4SE820<br />

(FF1760)<br />

62 62<br />

62 62<br />

46<br />

2<br />

clock input<br />

14<br />

9<br />

9<br />

184<br />

9<br />

9<br />

48 48<br />

48<br />

48<br />

x14<br />

<strong>FPGA</strong> E<br />

Stratix 4<br />

4SE820<br />

(FF1760)<br />

MB [95:0]<br />

96<br />

9<br />

clock input<br />

1<br />

9<br />

9<br />

clock input<br />

186<br />

9<br />

9<br />

9<br />

9<br />

<strong>FPGA</strong> F<br />

Stratix 4<br />

4SE820<br />

(FF1760)<br />

62 62<br />

62 62<br />

62 62 62 62<br />

46<br />

1<br />

2<br />

5<br />

14<br />

17<br />

mac addr<br />

Flash<br />

(24C64)<br />

8<br />

User<br />

Serial Flash<br />

(16 Mbit)<br />

x14<br />

122<br />

+2.5V<br />

I/O<br />

Main Bus<br />

Connector<br />

DDR2 SODIMM<br />

(4GB Max)<br />

114.285MHz<br />

<strong>FPGA</strong><br />

clock<br />

sourcing<br />

clk_TP<br />

single step clock<br />

(from config<br />

<strong>FPGA</strong>)<br />

clk_G0<br />

from config <strong>FPGA</strong><br />

48 MHz<br />

24<br />

MHz<br />

24<br />

MHz<br />

24<br />

MHz<br />

Clock Synth<br />

Si5326<br />

2Khz to 600MHz<br />

114.285MHz<br />

Clock Synth<br />

Si5326<br />

2Khz to 600MHz<br />

114.285MHz<br />

Clock Synth<br />

Si5326<br />

2Khz to 600MHz<br />

MB clock<br />

clk_G0<br />

(General<br />

clocking)<br />

clk_G1<br />

(DDR2)<br />

clk_G2<br />

(LVDS)<br />

clk_MB48<br />

DDR2 SODIMM<br />

(4GB Max)<br />

QL5064<br />

122<br />

89 89<br />

PCIe Express<br />

Endpoint<br />

<strong>FPGA</strong> A<br />

Stratix 4<br />

4SE820<br />

(FF1760)<br />

(250 MHz)<br />

clock input<br />

184<br />

9<br />

9<br />

9<br />

9<br />

3<br />

User<br />

Serial Flash<br />

(16 Mbit)<br />

x3<br />

5<br />

1<br />

<strong>FPGA</strong> B<br />

Stratix 4<br />

4SE820<br />

(FF1760)<br />

MICTOR<br />

clock input<br />

184<br />

x11<br />

clock input<br />

45<br />

User<br />

Serial Flash<br />

(16 Mbit)<br />

45<br />

45<br />

45<br />

21<br />

1<br />

21<br />

5<br />

21<br />

21<br />

<strong>FPGA</strong> C<br />

Stratix 4<br />

4SE820<br />

(FF1760)<br />

11<br />

x11<br />

34<br />

122<br />

MICTOR<br />

DDR2 SODIMM<br />

(4GB Max)<br />

Daughter card D<br />

clk_EXT0<br />

sma<br />

Daughter card F<br />

Daughter card E<br />

clk_EXT1<br />

PCI Express<br />

8 - lane<br />

GEN1 - 2.5 Gb/s (8-lanes)<br />

GEN2 - 5.0 Gb/s (4-lanes)<br />

= LVDS when paired, but can be used<br />

single-ended at reduced frequency<br />

Features<br />

PCIe endpoint<br />

clk_ref<br />

Global Clocks to all <strong>FPGA</strong>’s<br />

• PCI Express (8-lane) logic prototyping system with 2-6<br />

Altera Stratix-4 <strong>FPGA</strong>s<br />

- EP4SE820-3, -2 (slowest to fastest)<br />

- EP4SE530-3, -2<br />

• FF1760 package: 1,120 I/Os (with 4SE820)<br />

• Fixed 8-lane PCIe interface and controller provided<br />

- PCIe GEN1 rev 1.1<br />

- PCIe GEN2 with upgrade<br />

• 40+ million ASIC gates (ASIC measure) when stuffed with 6 Stratix-4 4SE820s<br />

• <strong>FPGA</strong> to <strong>FPGA</strong> interconnect is a mix of single-ended and LVDS<br />

- 600 MHz LVDS chip to chip (1.2 Gb/s)<br />

- LVDS pairs can be used as two single-ended signals at<br />

reduced frequency (~225MHz)<br />

- Reference designs for integrated I/O pad ISERDES/OSERDES<br />

- 10x pin multiplexing per LVDS pair<br />

- Greatly simplified logic partitioning<br />

- Source synchronous clocking for LVDS<br />

• Main Bus (MB) connects all Stratix-4 <strong>FPGA</strong>s (96 signals)<br />

- Single-ended<br />

• Auspy models for partitioning assistance<br />

• 4 separate DDR2 SODIMMs (350MHz)<br />

- Direct connection to <strong>FPGA</strong>s A, C, F, D<br />

- PC2-4200 or better<br />

- Addressing/power to support 4GB in each socket<br />

- DDR2 Verilog/VHDL reference design provided (no charge)<br />

- DDR2 SODIMM data transfer rate: 32Gb/s<br />

- Alternate pin compatible memory cards available<br />

(consult factory for availability):<br />

• SRAM: QDR, ASYNC, STD, or PSRAM, FLASH<br />

• DRAM: SDR, DDR1, PSRAM or RLDRAM, DDR3<br />

• Mictor, USB PHY, Extra Interconnect<br />

• Seven independent low-skew global clock networks<br />

- G0, G1, G2, M48, EXT0, EXT1, REF<br />

- Three, high-resolution, user-programmable synthesizers for G0, G1, G2<br />

- User configurable via CompactFLASH, USB, and/or PCIe<br />

- All seven global clocks networks distributed differentially and balanced<br />

• Two independent single-step clocks<br />

- Seven independent external clocks inputs (single-ended<br />

or differential) can be injected onto low-skew global clock networks<br />

Stratix IV<br />

<strong>FPGA</strong><br />

Speed<br />

Grades<br />

(slowest to<br />

fastest)<br />

LUT<br />

Size<br />

FF's<br />

Gate Estimate<br />

Max<br />

(100% util)<br />

(1000's)<br />

Practical<br />

(60% util)<br />

(1000's)<br />

• Flexible customization via daughter cards using expansion connectors<br />

- 3 daughter card locations: <strong>FPGA</strong>s D, E, F<br />

- 400-pin FCI MEG-Array connectors<br />

- 93 LVDS unidirectional pairs + clocks (or 186 single-ended)<br />

- 450MHz on all signals with source synchronous LVDS<br />

- Signal voltage set by daughter card (1.2v to 3.3V)<br />

- Reset<br />

- Supplied power rails (fused):<br />

• +12v (24W max)<br />

• +5V (10W max)<br />

• +3.3V (10W max)<br />

- Pin multiplexing to/from daughter cards using LVDS (up to 10x)<br />

• Fast and Painless <strong>FPGA</strong> configuration<br />

- CompactFLASH, USB, PCIe, JTAG<br />

- Configuration Error reporting<br />

- Accelerated configuration readback<br />

• RS232 port for embedded uP debug<br />

- Accessible from all <strong>FPGA</strong>s via separate 2-signal bus<br />

• Full support for embedded logic analyzers via JTAG interface<br />

- SignalTap, and other third-party debug solutions<br />

• 54 status <strong>FPGA</strong>-controller LEDs: bright enough to<br />

illuminate airplane landing strips<br />

Max I/O's<br />

MLAB<br />

(640)<br />

M9K<br />

(9 kbit)<br />

M144K<br />

(144 kbit)<br />

Total<br />

(kbits)<br />

Total<br />

(kbytes)<br />

4SE820 -4,-3 6-input 656,000 10,496 6,508 1120 960 16261 1610 60 23,130 2,891<br />

4SE530 -4,-3,-2 6-input 424,960 6,799 4,080 960 1024 10624 1280 64 20,736 2,592<br />

Multipliers<br />

(18x18)<br />

Memory<br />

858 . 454 . 3419 21