Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

DC2<br />

DC3<br />

SMA<br />

SMA<br />

20<br />

96<br />

96<br />

20<br />

DDR2 SODIMM<br />

(4GB max)<br />

120 120 120 96 96<br />

<strong>FPGA</strong><br />

0<br />

Virtex-5<br />

LX330<br />

(FF1760)<br />

240 240<br />

<strong>FPGA</strong><br />

4<br />

Virtex-5<br />

LX330<br />

(FF1760)<br />

120 120<br />

<strong>FPGA</strong><br />

8<br />

Virtex-5<br />

LX330<br />

(FF1760)<br />

120 120<br />

<strong>FPGA</strong><br />

12<br />

Virtex-5<br />

LX330<br />

(FF1760)<br />

160<br />

20 20<br />

20 20<br />

120<br />

20 20<br />

20 20<br />

120<br />

20 20<br />

20 20<br />

160<br />

120 120<br />

120 120<br />

120 120<br />

20 20<br />

20 20<br />

20 20<br />

20 20<br />

20 20<br />

20 20<br />

120 120 120<br />

DDR2 SODIMM<br />

(4GB max)<br />

DIMM0 DIMM1 DIMM2<br />

DIMM3<br />

Serial<br />

FLASH<br />

128Mb<br />

Serial<br />

FLASH<br />

128Mb<br />

DDR2 SODIMM<br />

(4GB max)<br />

<strong>FPGA</strong><br />

1<br />

Virtex-5<br />

LX330<br />

(FF1760)<br />

<strong>FPGA</strong><br />

5<br />

Virtex-5<br />

LX330<br />

(FF1760)<br />

<strong>FPGA</strong><br />

9<br />

Virtex-5<br />

LX330<br />

(FF1760)<br />

<strong>FPGA</strong><br />

13<br />

Virtex-5<br />

LX330<br />

(FF1760)<br />

DDR2 SODIMM<br />

(4GB max)<br />

DIMM4<br />

Serial<br />

FLASH<br />

128Mb<br />

Serial<br />

FLASH<br />

128Mb<br />

120<br />

80<br />

80<br />

120<br />

DDR2 SODIMM<br />

(4GB max)<br />

<strong>FPGA</strong><br />

2<br />

Virtex-5<br />

LX330<br />

(FF1760)<br />

1 0 1 0<br />

<strong>FPGA</strong><br />

6<br />

Virtex-5<br />

LX330<br />

(FF1760)<br />

1 0 1 0<br />

<strong>FPGA</strong><br />

10<br />

Virtex-5<br />

LX330<br />

(FF1760)<br />

1 0 100<br />

<strong>FPGA</strong><br />

14<br />

Virtex-5<br />

LX330<br />

(FF1760)<br />

DDR2 SODIMM<br />

(4GB max)<br />

DIMM5<br />

Serial<br />

FLASH<br />

128Mb<br />

MBV<br />

20 20<br />

20 20<br />

20 20<br />

20 20<br />

20 20<br />

20 20<br />

Serial<br />

FLASH<br />

128Mb<br />

140<br />

80<br />

120<br />

120<br />

140<br />

SMA<br />

SMA<br />

+1.5V to +3.3V I/O<br />

DC4<br />

MEG Array Expansion<br />

Connector (400-pin)<br />

<strong>FPGA</strong><br />

3<br />

Virtex-5<br />

LX330<br />

(FF1760)<br />

1 0 100<br />

<strong>FPGA</strong><br />

7<br />

Virtex-5<br />

LX330<br />

(FF1760)<br />

1 0<br />

1 0<br />

<strong>FPGA</strong><br />

11<br />

Virtex-5<br />

LX330<br />

(FF1760)<br />

1 0 1 0<br />

<strong>FPGA</strong><br />

15<br />

Virtex-5<br />

LX330<br />

(FF1760)<br />

96 96<br />

MEG Array Expansion<br />

Connector (400-pin)<br />

DC9<br />

+1.5V to +3.3V I/O<br />

96<br />

MBH<br />

96<br />

96<br />

MBH<br />

96<br />

SMA<br />

MEG Array Expansion<br />

Connector (400-pin)<br />

+1.5V to +3.3V I/O<br />

DC5<br />

MEG Array Expansion<br />

Connector (400-pin)<br />

+1.5V to +3.3V I/O<br />

QuickSwitch<br />

DC6<br />

MEG Array Expansion<br />

MEG Array Expansion<br />

Connector (400-pin)<br />

Connector (400-pin)<br />

+1.5V to +3.3V I/O<br />

+1.5V to +3.3V I/O<br />

QuickSwitch<br />

DC7<br />

DC8<br />

SMA<br />

80<br />

(quickswitches)<br />

MBH<br />

MICTOR<br />

Control<br />

32<br />

CY7C68013<br />

uP Configuration<br />

controller<br />

Clock Mux<br />

Control<br />

MBCLK<br />

Reference Clock<br />

GCLK0<br />

GCLK1<br />

GCLK2<br />

DC_GCLK0<br />

DC_GCLK1<br />

DC_GCLK2<br />

DC_GCLK3<br />

SRAM<br />

128Kb x 8<br />

Flash<br />

1 M x 8<br />

Config<br />

<strong>FPGA</strong><br />

LX80<br />

(FF1148)<br />

Single-Step Clock<br />

JTAG<br />

USB 2.0<br />

48 MHz<br />

8<br />

RS232<br />

4 Serial<br />

Ports<br />

(Tx/Rx)<br />

COMPACT FLASH<br />

<strong>FPGA</strong><br />

CONFIGURATION<br />

Reset<br />

96<br />

MEG Array Expansion<br />

Connector (400-pin)<br />

+1.5V to +3.3V I/O<br />

Config PROM<br />

LCD<br />

Control<br />

Panel<br />

PCI0<br />

Clock Synth<br />

Si5326<br />

Clock Synth<br />

Si5326<br />

External<br />

Clock SMA's<br />

Clock Synth<br />

Si5326<br />

External<br />

Clock SMA's<br />

Clock Synth<br />

Si5326<br />

External<br />

Clock SMA's<br />

from Daughter Card 2 (DC2)<br />

from Daughter Card 4 (DC4)<br />

from Daughter Card 3 (DC3)<br />

from Daughter Card 9 (DC9)<br />

from Daughter Card 5 (DC5)<br />

from Daughter Card 6 (DC6)<br />

from Daughter Card 7 (DC7)<br />

from Daughter Card 8 (DC8)<br />

LED<br />

(x32)<br />

104<br />

104<br />

32<br />

20<br />

32<br />

32<br />

32<br />

30<br />

29<br />

(USB 3300)<br />

40-pin<br />

IDC Headers<br />

(x5)<br />

Config<br />

EEPROM<br />

RJ45<br />

2<br />

3<br />

3<br />

15<br />

32<br />

7<br />

22<br />

16<br />

4<br />

36<br />

16<br />

SDRAM<br />

16M x 32<br />

FLASH<br />

(32/64 MBIT)<br />

(AT<br />

49BV320D)<br />

2M x 16<br />

SSRAM<br />

(512k x 36)<br />

CY7C<br />

1380D<br />

SoundMAX<br />

Codec<br />

(AD1881A)<br />

<strong>FPGA</strong><br />

CD Audio<br />

Line Out<br />

Headphone<br />

In<br />

EE<br />

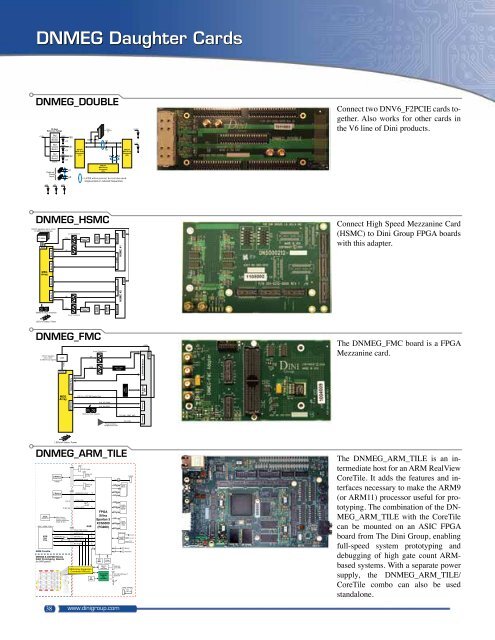

DNMEG Daughter Cards<br />

DNMEG_DOUBLE<br />

+3.3V<br />

I/O Bank<br />

Reference Voltage<br />

Ref +2.5V<br />

VCCO<br />

Bank0<br />

LED<br />

Ref<br />

VCCO<br />

Bank1<br />

Ref<br />

VCCO<br />

Bank2<br />

500mA<br />

B0<br />

+2.5V<br />

B1<br />

LED<br />

+2.5V<br />

B2<br />

LED<br />

400-pin<br />

MEG-Array<br />

Connector<br />

(P1)<br />

93 93<br />

93<br />

93<br />

93 93<br />

400-pin<br />

MEG-Array<br />

Connector<br />

(P2)<br />

B_RST<br />

T_RST<br />

Connect two DNV6_F2PCIE cards together.<br />

Also works for other cards in<br />

the V6 line of <strong>Dini</strong> products.<br />

External<br />

Clock<br />

Input<br />

p1<br />

p2<br />

400-pin<br />

MEG-Array<br />

Connector<br />

(P3)<br />

= LVDS when paired, but can be used<br />

single-ended at reduced frequencies<br />

+12V<br />

+5V +3.3V<br />

DNMEG_HSMC<br />

(VCCO regulators set to +2.5V,<br />

for MEG Array Signals)<br />

LT1963A<br />

Power<br />

MEG<br />

Array<br />

Bank #1 Bank #3 Bank #2 Bank #0<br />

JTAG<br />

IIC<br />

IIC<br />

(Level Translators)<br />

Altera JTAG<br />

Header<br />

Probe<br />

Points<br />

Probe<br />

Points<br />

HS Serial<br />

LVDS<br />

LVDS<br />

HSMC #1<br />

HSMC #2<br />

Power Power<br />

Connect High Speed Mezzanine Card<br />

(HSMC) to <strong>Dini</strong> <strong>Group</strong> <strong>FPGA</strong> boards<br />

with this adapter.<br />

SMAs for GCC Insertion<br />

JTAG<br />

Altera JTAG<br />

Header<br />

Probe<br />

Points<br />

Probe<br />

Points<br />

HS Serial<br />

(Level Translators)<br />

LEDs for Status, Power<br />

DNMEG_FMC<br />

(VCCO regulators<br />

set to +2.5V, LDO<br />

for MEG Array Signals)<br />

+VADJ<br />

Power<br />

(Level Translators)<br />

IIC<br />

JTAG<br />

Xilinx JTAG<br />

Header<br />

LA/HA/HB Banks<br />

+VADJ<br />

Power<br />

<strong>The</strong> DNMEG_FMC board is a <strong>FPGA</strong><br />

Mezzanine card.<br />

MEG<br />

Array<br />

SelectIO Pins<br />

+VIO (VCCO FOR HB Signals Only)<br />

QSE<br />

Headers<br />

HS Serial<br />

(DP)<br />

Clocking<br />

CLK_UP (C2M)<br />

CLK_DN (M2C)<br />

SMAs for Clock Insertion<br />

PG_M2C, PSNT_M2C<br />

PG_C2M<br />

Power monitors,<br />

daughtercard reset<br />

Clocking Sideband<br />

DNMEG_ARM_TILE<br />

CPLD<br />

(XC9572)<br />

ARM7 / ARM9 / ARM 11<br />

ARM<br />

Test<br />

Chip<br />

38<br />

LEDs for Status, Power<br />

Z Memory<br />

Expansion<br />

PISMO<br />

Y Memory<br />

Expansion<br />

PISMO<br />

ARM Coretile<br />

DN9000 & DN7000 Series<br />

ASIC Prototyping <strong>Boards</strong><br />

(to 50M gates)<br />

MEG Array Expansion<br />

Connector (400-pin)<br />

+1.5V to +3.3V I/O<br />

MEG Array Expansion<br />

Connector (400-pin)<br />

+1.5V to +3.3V I/O<br />

Y[31:0]<br />

Y[169:150]<br />

Misc Control<br />

(power, clocks,<br />

memory type/sizes,<br />

board ID, etc.)<br />

HWDATA[31:0]<br />

HDRZ<br />

HDRY<br />

JTAG<br />

MEMEXPB [103:0]<br />

MEMEXPA [103:0]<br />

<strong>FPGA</strong>_LED<br />

<strong>FPGA</strong>_GPIO<br />

CPLD Config<br />

JTAG<br />

ARM ICE<br />

Config<br />

ARM ICE<br />

Debug<br />

JTAG<br />

AHB<br />

HDRX<br />

Clocks, Misc control<br />

HADDR[31:0]<br />

HDATA[31:0]<br />

HRDATA[31:0]<br />

Bus Control<br />

MEG Array Expansion<br />

Connector (400-pin)<br />

25<br />

MHz<br />

<strong>FPGA</strong><br />

Xilinx<br />

Spartan 3<br />

XCS5000<br />

(FG900)<br />

100<br />

MHz<br />

USB-OTG<br />

Phy<br />

10/100/1000<br />

Ethernet<br />

Phy<br />

(UCS8601)<br />

Addr<br />

Data<br />

Addr<br />

Data<br />

Addr<br />

USB 2.0<br />

(mini AB)<br />

www.dinigroup.com<br />

Cntl<br />

Cntl<br />

Data<br />

Cntl<br />

AC97 Audio<br />

10/100/1000 base T<br />

Ethernet<br />

RS232<br />

Mouse<br />

Keyboard<br />

JTAG (<strong>FPGA</strong>)<br />

<strong>The</strong> DNMEG_ARM_TILE is an intermediate<br />

host for an ARM RealView<br />

CoreTile. It adds the features and interfaces<br />

necessary to make the ARM9<br />

(or ARM11) processor useful for prototyping.<br />

<strong>The</strong> combination of the DN-<br />

MEG_ARM_TILE with the CoreTile<br />

can be mounted on an ASIC <strong>FPGA</strong><br />

board from <strong>The</strong> <strong>Dini</strong> <strong>Group</strong>, enabling<br />

full-speed system prototyping and<br />

debugging of high gate count ARMbased<br />

systems. With a separate power<br />

supply, the DNMEG_ARM_TILE/<br />

CoreTile combo can also be used<br />

standalone.