P89V51RB2/RC2/RD2 8-bit 80C51 5 V low power 16/32 ... - NetMedia

P89V51RB2/RC2/RD2 8-bit 80C51 5 V low power 16/32 ... - NetMedia

P89V51RB2/RC2/RD2 8-bit 80C51 5 V low power 16/32 ... - NetMedia

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

NXP Semiconductors<br />

<strong>P89V51RB2</strong>/<strong>RC2</strong>/<strong>RD2</strong><br />

8-<strong>bit</strong> microcontrollers with <strong>80C51</strong> core<br />

Table 64. External clock drive<br />

Symbol Parameter Oscillator Unit<br />

40 MHz Variable<br />

Min Max Min Max<br />

f osc oscillator frequency - - 0 40 MHz<br />

T cy(clk) clock cycle time 25 - - - ns<br />

t CHCX clock HIGH time 8.75 - 0.35T cy(clk) 0.65T cy(clk) ns<br />

t CLCX clock LOW time 8.75 - 0.35T cy(clk) 0.65T cy(clk) ns<br />

t CLCH clock rise time - 10 - - ns<br />

t CHCL clock fall time - 10 - - ns<br />

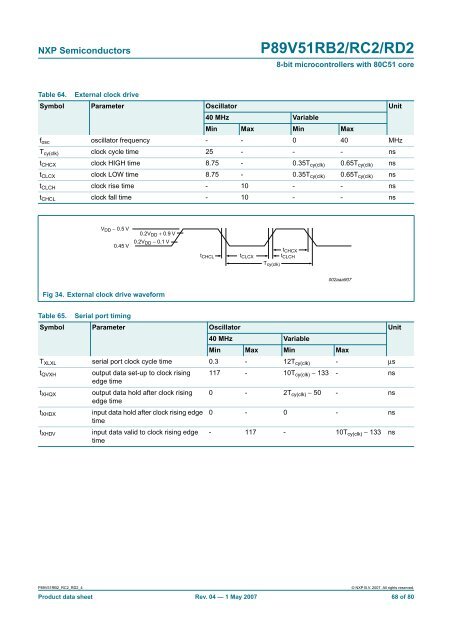

V DD − 0.5 V<br />

0.45 V<br />

0.2V DD + 0.9 V<br />

0.2V DD − 0.1 V<br />

t CHCL t CLCX t CLCH<br />

T cy(clk)<br />

t CHCX<br />

002aaa907<br />

Fig 34. External clock drive waveform<br />

Table 65.<br />

Serial port timing<br />

Symbol Parameter Oscillator Unit<br />

40 MHz Variable<br />

Min Max Min Max<br />

T XLXL serial port clock cycle time 0.3 - 12T cy(clk) - µs<br />

t QVXH<br />

output data set-up to clock rising 117 - 10T cy(clk) − 133 - ns<br />

edge time<br />

t XHQX<br />

output data hold after clock rising 0 - 2T cy(clk) − 50 - ns<br />

edge time<br />

t XHDX<br />

input data hold after clock rising edge 0 - 0 - ns<br />

time<br />

t XHDV<br />

input data valid to clock rising edge<br />

time<br />

- 117 - 10T cy(clk) − 133 ns<br />

<strong>P89V51RB2</strong>_<strong>RC2</strong>_<strong>RD2</strong>_4<br />

© NXP B.V. 2007. All rights reserved.<br />

Product data sheet Rev. 04 — 1 May 2007 68 of 80