P89V51RB2/RC2/RD2 8-bit 80C51 5 V low power 16/32 ... - NetMedia

P89V51RB2/RC2/RD2 8-bit 80C51 5 V low power 16/32 ... - NetMedia

P89V51RB2/RC2/RD2 8-bit 80C51 5 V low power 16/32 ... - NetMedia

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

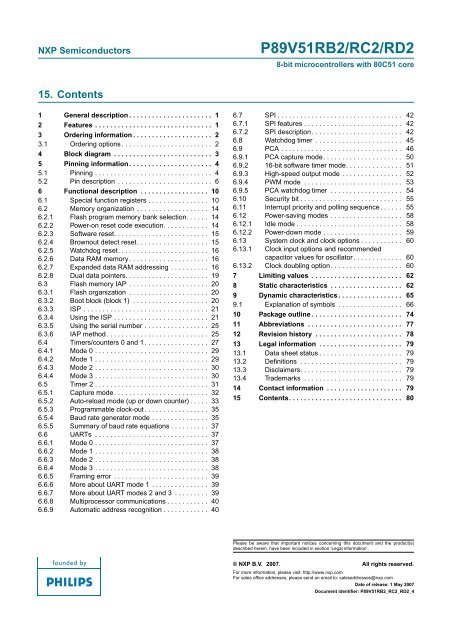

NXP Semiconductors<br />

<strong>P89V51RB2</strong>/<strong>RC2</strong>/<strong>RD2</strong><br />

8-<strong>bit</strong> microcontrollers with <strong>80C51</strong> core<br />

15. Contents<br />

1 General description . . . . . . . . . . . . . . . . . . . . . . 1<br />

2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1<br />

3 Ordering information . . . . . . . . . . . . . . . . . . . . . 2<br />

3.1 Ordering options . . . . . . . . . . . . . . . . . . . . . . . . 2<br />

4 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . 3<br />

5 Pinning information . . . . . . . . . . . . . . . . . . . . . . 4<br />

5.1 Pinning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4<br />

5.2 Pin description . . . . . . . . . . . . . . . . . . . . . . . . . 6<br />

6 Functional description . . . . . . . . . . . . . . . . . . 10<br />

6.1 Special function registers . . . . . . . . . . . . . . . . 10<br />

6.2 Memory organization . . . . . . . . . . . . . . . . . . . 14<br />

6.2.1 Flash program memory bank selection. . . . . . 14<br />

6.2.2 Power-on reset code execution. . . . . . . . . . . . 14<br />

6.2.3 Software reset. . . . . . . . . . . . . . . . . . . . . . . . . 15<br />

6.2.4 Brownout detect reset. . . . . . . . . . . . . . . . . . . 15<br />

6.2.5 Watchdog reset. . . . . . . . . . . . . . . . . . . . . . . . <strong>16</strong><br />

6.2.6 Data RAM memory . . . . . . . . . . . . . . . . . . . . . <strong>16</strong><br />

6.2.7 Expanded data RAM addressing . . . . . . . . . . <strong>16</strong><br />

6.2.8 Dual data pointers. . . . . . . . . . . . . . . . . . . . . . 19<br />

6.3 Flash memory IAP . . . . . . . . . . . . . . . . . . . . . 20<br />

6.3.1 Flash organization . . . . . . . . . . . . . . . . . . . . . 20<br />

6.3.2 Boot block (block 1) . . . . . . . . . . . . . . . . . . . . 20<br />

6.3.3 ISP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21<br />

6.3.4 Using the ISP . . . . . . . . . . . . . . . . . . . . . . . . . 21<br />

6.3.5 Using the serial number . . . . . . . . . . . . . . . . . 25<br />

6.3.6 IAP method. . . . . . . . . . . . . . . . . . . . . . . . . . . 25<br />

6.4 Timers/counters 0 and 1. . . . . . . . . . . . . . . . . 27<br />

6.4.1 Mode 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29<br />

6.4.2 Mode 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29<br />

6.4.3 Mode 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30<br />

6.4.4 Mode 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30<br />

6.5 Timer 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31<br />

6.5.1 Capture mode. . . . . . . . . . . . . . . . . . . . . . . . . <strong>32</strong><br />

6.5.2 Auto-reload mode (up or down counter) . . . . . 33<br />

6.5.3 Programmable clock-out . . . . . . . . . . . . . . . . . 35<br />

6.5.4 Baud rate generator mode . . . . . . . . . . . . . . . 35<br />

6.5.5 Summary of baud rate equations . . . . . . . . . . 37<br />

6.6 UARTs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37<br />

6.6.1 Mode 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37<br />

6.6.2 Mode 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38<br />

6.6.3 Mode 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38<br />

6.6.4 Mode 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38<br />

6.6.5 Framing error . . . . . . . . . . . . . . . . . . . . . . . . . 39<br />

6.6.6 More about UART mode 1 . . . . . . . . . . . . . . . 39<br />

6.6.7 More about UART modes 2 and 3 . . . . . . . . . 39<br />

6.6.8 Multiprocessor communications . . . . . . . . . . . 40<br />

6.6.9 Automatic address recognition . . . . . . . . . . . . 40<br />

6.7 SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42<br />

6.7.1 SPI features . . . . . . . . . . . . . . . . . . . . . . . . . . 42<br />

6.7.2 SPI description . . . . . . . . . . . . . . . . . . . . . . . . 42<br />

6.8 Watchdog timer . . . . . . . . . . . . . . . . . . . . . . . 45<br />

6.9 PCA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46<br />

6.9.1 PCA capture mode. . . . . . . . . . . . . . . . . . . . . 50<br />

6.9.2 <strong>16</strong>-<strong>bit</strong> software timer mode. . . . . . . . . . . . . . . 51<br />

6.9.3 High-speed output mode . . . . . . . . . . . . . . . . 52<br />

6.9.4 PWM mode . . . . . . . . . . . . . . . . . . . . . . . . . . 53<br />

6.9.5 PCA watchdog timer . . . . . . . . . . . . . . . . . . . 54<br />

6.10 Security <strong>bit</strong> . . . . . . . . . . . . . . . . . . . . . . . . . . . 55<br />

6.11 Interrupt priority and polling sequence. . . . . . 55<br />

6.12 Power-saving modes . . . . . . . . . . . . . . . . . . . 58<br />

6.12.1 Idle mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58<br />

6.12.2 Power-down mode . . . . . . . . . . . . . . . . . . . . . 59<br />

6.13 System clock and clock options . . . . . . . . . . . 60<br />

6.13.1 Clock input options and recommended<br />

capacitor values for oscillator . . . . . . . . . . . . . 60<br />

6.13.2 Clock doubling option . . . . . . . . . . . . . . . . . . . 60<br />

7 Limiting values . . . . . . . . . . . . . . . . . . . . . . . . 62<br />

8 Static characteristics . . . . . . . . . . . . . . . . . . . 62<br />

9 Dynamic characteristics . . . . . . . . . . . . . . . . . 65<br />

9.1 Explanation of symbols . . . . . . . . . . . . . . . . . 66<br />

10 Package outline . . . . . . . . . . . . . . . . . . . . . . . . 74<br />

11 Abbreviations . . . . . . . . . . . . . . . . . . . . . . . . . 77<br />

12 Revision history . . . . . . . . . . . . . . . . . . . . . . . 78<br />

13 Legal information . . . . . . . . . . . . . . . . . . . . . . 79<br />

13.1 Data sheet status . . . . . . . . . . . . . . . . . . . . . . 79<br />

13.2 Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . 79<br />

13.3 Disclaimers. . . . . . . . . . . . . . . . . . . . . . . . . . . 79<br />

13.4 Trademarks . . . . . . . . . . . . . . . . . . . . . . . . . . 79<br />

14 Contact information . . . . . . . . . . . . . . . . . . . . 79<br />

15 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80<br />

Please be aware that important notices concerning this document and the product(s)<br />

described herein, have been included in section ‘Legal information’.<br />

© NXP B.V. 2007. All rights reserved.<br />

For more information, please visit: http://www.nxp.com<br />

For sales office addresses, please send an email to: salesaddresses@nxp.com<br />

Date of release: 1 May 2007<br />

Document identifier: <strong>P89V51RB2</strong>_<strong>RC2</strong>_<strong>RD2</strong>_4