Sequential Circuits Prophet-5 Service Manual - Audiofanzine

Sequential Circuits Prophet-5 Service Manual - Audiofanzine

Sequential Circuits Prophet-5 Service Manual - Audiofanzine

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

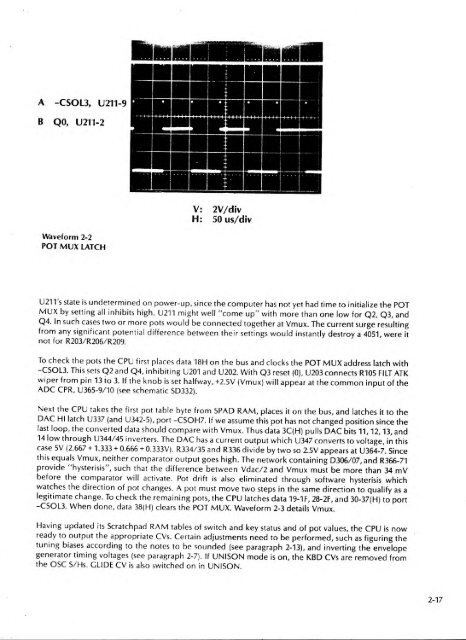

1A -CSOL3, U211-9B QO, U211-2V:H:2V/dlv50 us/divWaveform 2-2POT MUX LATCHU211's state is undetermined on power-up, since the computer has not yet had time to initialize the POTMUX by setting aii inhibits high. U211 might well "come up" with more than one low for Q2, Q3, andQ4. In such cases two or more pots would be connected together at Vmux. The current surge resultingfrom any significant potential difference between their settings would instantly destroy a 4051, were itnot for R203/R206/R209.To check the pots the CPU first places data 18H on the bus and clocks the POT MUX address latch with-CSOL3. This sets Q2 and Q4, inhibiting U201 and U202. With Q3 reset (0),U203 connects R105 FILT ATKwiper from pin 13 to 3. If the knob is set halfway, +2.5V (Vmux) will appear at the common input of theADC CPR, U365-9/10 (see schematic SD332).Next the CPU takes the first pot table byte from SPAD RAM, places it on the bus, and latches it to theDAC HI latch U337 (and U342-5), port -CSOH7. If we assume this pot has not changed position since the'ast loop, the converted data should compare with Vmux. Thus data 3C(H) pulls DAC bits 11, 12, 13, and14 low through U344/45 inverters. The DAC has a current output which U347 converts to voltage, in thiscase 5V (2.667 + 1.333 + 0.666 + 0.333V). R334/35 and R336 divide by two so 2.5V appears at U364-7. Sincethis equals Vmux, neither comparator output goes high. The network containing D306/07, and R366-71provide ''hysterisis", such that the difference between Vdac/2 and Vmux must be more than 34 mVbefore the comparator will activate. Pot drift is also eliminated through software hysterisis whichwatches the direction of pot changes. A pot must move two steps in the same direction to qualify as alegitimate change. To check the remaining pots, the CPU latches data 19-1F, 28-2F, and 30-37(H) to port-CSOL3. When done, data 38(H) clears the POT MUX. Waveform 2-3 details Vmux.Having updated its Scratchpad RAM tables of switch and key status and of pot values, the CPU is nowready to output the appropriate CVs. Certain adjustments need to be performed, such as figuring thetuning biases according to the notes to be sounded (see paragraph 2-13), and inverting the envelopegenerator timing voltages (see paragraph 2-7). If UNISON mode is on, the KBD CVs are removed fromthe OSC S/Hs. GLIDE CV is also switched on in UNISON2-17