LECTURE 040 –DIGITAL PHASE LOCK LOOPS (DPLLs)

LECTURE 040 –DIGITAL PHASE LOCK LOOPS (DPLLs)

LECTURE 040 –DIGITAL PHASE LOCK LOOPS (DPLLs)

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

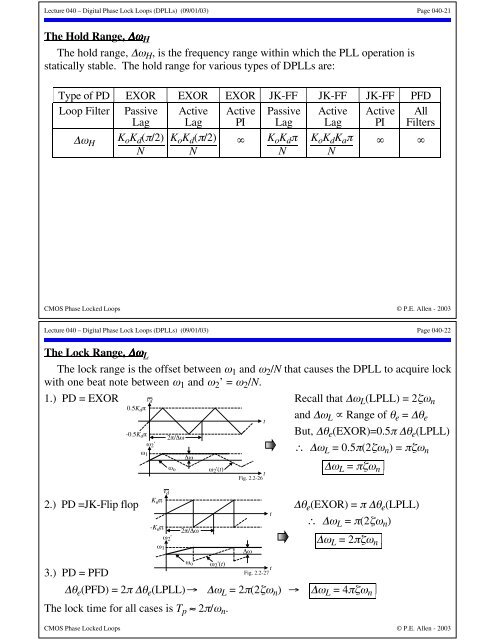

Lecture <strong>040</strong> – Digital Phase Lock Loops (<strong>DPLLs</strong>) (09/01/03) Page <strong>040</strong>-21The Hold Range, ∆ω HThe hold range, ∆ω H , is the frequency range within which the PLL operation isstatically stable. The hold range for various types of <strong>DPLLs</strong> are:Type of PD EXOR EXOR EXOR JK-FF JK-FF JK-FF PFDLoop Filter PassiveLagActiveLagActivePIPassiveLagActiveLagActivePIAllFilters∆ω HK o K d (π/2) oK d (π/2) ∞ K o K d π K o K d K a πN NN N∞ ∞CMOS Phase Locked Loops © P.E. Allen - 2003Lecture <strong>040</strong> – Digital Phase Lock Loops (<strong>DPLLs</strong>) (09/01/03) Page <strong>040</strong>-22The Lock Range, ∆ω LThe lock range is the offset between ω 1 and ω 2 /N that causes the DPLL to acquire lockwith one beat note between ω 1 and ω 2 ’ = ω 2 /N.1.) PD = EXOR v d0.5K d πtRecall that ∆ω L (LPLL) = 2ζω nand ∆ω L ∝ Range of θ e = ∆θ e-0.5K d πω 2 'But, ∆θ e (EXOR)=0.5π ∆θ e (LPLL)2π/∆ω∴ ∆ω L = 0.5π(2ζω n ) = πζω nω 1v dK d πω o∆ω∆ω L = πζω n2.) PD =JK-Flip flop ∆θ e (EXOR) = π ∆θ e (LPLL)t∴ ∆ω L = π(2ζω n )-K d πω 2 'ω 12π/∆ωω o∆ω L = 2πζω n3.) PD = PFD∆θ e (PFD) = 2π ∆θ e (LPLL)→Fig. 2.2-27∆ω L = 2π(2ζω n ) → ∆ω L = 4πζω nThe lock time for all cases is T p ≈ 2π/ω n .ω 2 '(t)ω 2 '(t)tFig. 2.2-26∆ωCMOS Phase Locked Loops © P.E. Allen - 2003t