LECTURE 040 –DIGITAL PHASE LOCK LOOPS (DPLLs)

LECTURE 040 –DIGITAL PHASE LOCK LOOPS (DPLLs)

LECTURE 040 –DIGITAL PHASE LOCK LOOPS (DPLLs)

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

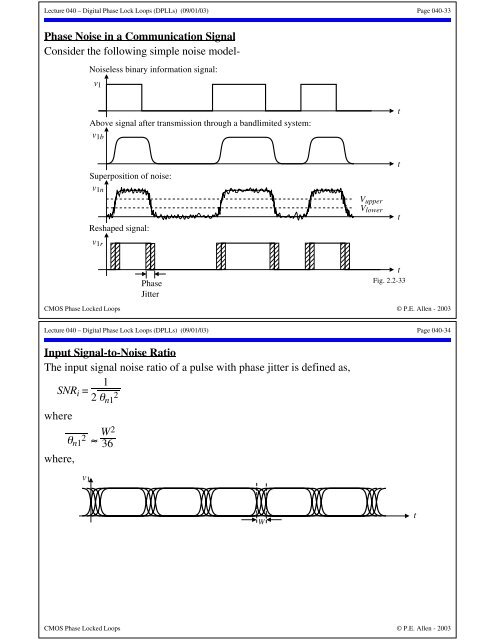

Lecture <strong>040</strong> – Digital Phase Lock Loops (<strong>DPLLs</strong>) (09/01/03) Page <strong>040</strong>-33Phase Noise in a Communication SignalConsider the following simple noise model-Noiseless binary information signal:v 1Above signal after transmission through a bandlimited system:v 1btSuperposition of noise:v 1nReshaped signal:v;;1r;;;;PhaseJitter;; ;;;;;; ;;;;V upperV lowerCMOS Phase Locked Loops © P.E. Allen - 2003tttFig. 2.2-33Lecture <strong>040</strong> – Digital Phase Lock Loops (<strong>DPLLs</strong>) (09/01/03) Page <strong>040</strong>-34Input Signal-to-Noise RatioThe input signal noise ratio of a pulse with phase jitter is defined as,1SNR i =2 θ 2 n1whereθ 2 n1 ≈ W236where,v 1WtCMOS Phase Locked Loops © P.E. Allen - 2003