LECTURE 040 –DIGITAL PHASE LOCK LOOPS (DPLLs)

LECTURE 040 –DIGITAL PHASE LOCK LOOPS (DPLLs)

LECTURE 040 –DIGITAL PHASE LOCK LOOPS (DPLLs)

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

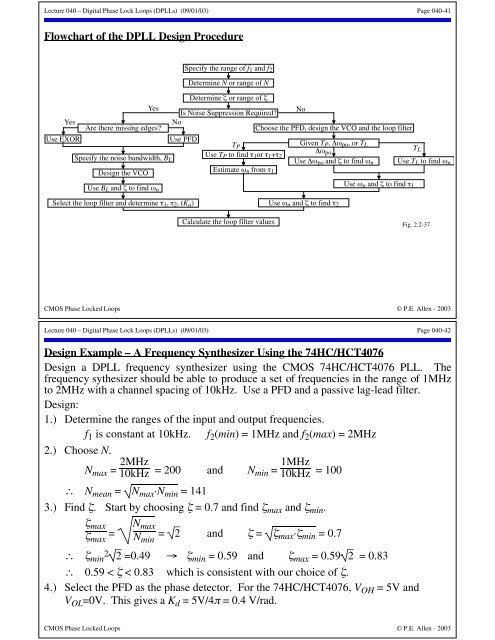

Lecture <strong>040</strong> – Digital Phase Lock Loops (<strong>DPLLs</strong>) (09/01/03) Page <strong>040</strong>-41Flowchart of the DPLL Design ProcedureYesUse EXORYesAre there missing edges?Specify the noise bandwidth, B LDesign the VCOSpecify the range of f 1 and f 2Determine N or range of NDetermine ζ or range of ζNoIs Noise Suppression Required?NoChoose the PFD, design the VCO and the loop filterUse PFDTP Given T P , ∆ω po , or T L∆ω T po LUse T P to find τ 1 or τ 1 +τ 2Use ∆ω po and ζ to find ω n Use T L to find ω nEstimate ω n from τ 1Use ω n and ζ to find τ 1Use B L and ζ to find ω nSelect the loop filter and determine τ 1 , τ 2 , (K a )Use ω n and ζ to find τ 2Calculate the loop filter values Fig. 2.2-37CMOS Phase Locked Loops © P.E. Allen - 2003Lecture <strong>040</strong> – Digital Phase Lock Loops (<strong>DPLLs</strong>) (09/01/03) Page <strong>040</strong>-42Design Example – A Frequency Synthesizer Using the 74HC/HCT4076Design a DPLL frequency synthesizer using the CMOS 74HC/HCT4076 PLL. Thefrequency sythesizer should be able to produce a set of frequencies in the range of 1MHzto 2MHz with a channel spacing of 10kHz. Use a PFD and a passive lag-lead filter.Design:1.) Determine the ranges of the input and output frequencies.f 1 is constant at 10kHz. f 2 (min) = 1MHz and f 2 (max) = 2MHz2.) Choose N.N max = 2MHz10kHz = 200 and N min = 1MHz10kHz = 100∴ N mean = N max·N min = 1413.) Find ζ. Start by choosing ζ = 0.7 and find ζ max and ζ min .ζ maxζ max=N maxN min= 2 and ζ = ζ max·ζ min = 0.7∴ ζ 2 min 2 =0.49 → ζ min = 0.59 and ζ max = 0.59 2 = 0.83∴ 0.59 < ζ < 0.83 which is consistent with our choice of ζ.4.) Select the PFD as the phase detector. For the 74HC/HCT4076, V OH = 5V andV OL =0V. This gives a K d = 5V/4π = 0.4 V/rad.CMOS Phase Locked Loops © P.E. Allen - 2003