LECTURE 040 –DIGITAL PHASE LOCK LOOPS (DPLLs)

LECTURE 040 –DIGITAL PHASE LOCK LOOPS (DPLLs)

LECTURE 040 –DIGITAL PHASE LOCK LOOPS (DPLLs)

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

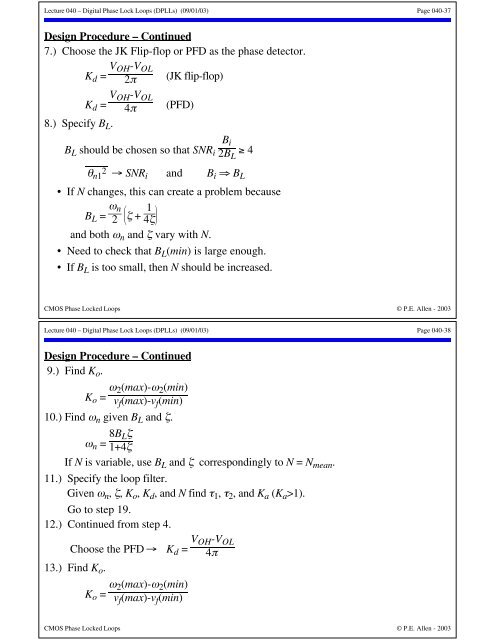

Lecture <strong>040</strong> – Digital Phase Lock Loops (<strong>DPLLs</strong>) (09/01/03) Page <strong>040</strong>-37Design Procedure – Continued7.) Choose the JK Flip-flop or PFD as the phase detector.K d = V OH-V OL2π (JK flip-flop)K d = V OH-V OL4π (PFD)8.) Specify B L .B L should be chosen so that SNR i B i2B L≥ 4θ n12 → SNR i and B i ⇒ B L• If N changes, this can create a problem becauseB L = ω n ⎛ ⎞⎜2 ζ + 1 ⎟⎝ 4ζ ⎠and both ω n and ζ vary with N.• Need to check that B L (min) is large enough.• If B L is too small, then N should be increased.CMOS Phase Locked Loops © P.E. Allen - 2003Lecture <strong>040</strong> – Digital Phase Lock Loops (<strong>DPLLs</strong>) (09/01/03) Page <strong>040</strong>-38Design Procedure – Continued9.) Find K o .K o = ω 2(max)-ω 2 (min)v f (max)-v f (min)10.) Find ω n given B L and ζ.ω n = 8B Lζ1+4ζIf N is variable, use B L and ζ correspondingly to N = N mean .11.) Specify the loop filter.Given ω n , ζ, K o , K d , and N find τ 1 , τ 2 , and K a (K a >1).Go to step 19.12.) Continued from step 4.Choose the PFD →13.) Find K o .K o = ω 2(max)-ω 2 (min)v f (max)-v f (min)K d = V OH-V OL4πCMOS Phase Locked Loops © P.E. Allen - 2003