LECTURE 040 –DIGITAL PHASE LOCK LOOPS (DPLLs)

LECTURE 040 –DIGITAL PHASE LOCK LOOPS (DPLLs)

LECTURE 040 –DIGITAL PHASE LOCK LOOPS (DPLLs)

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

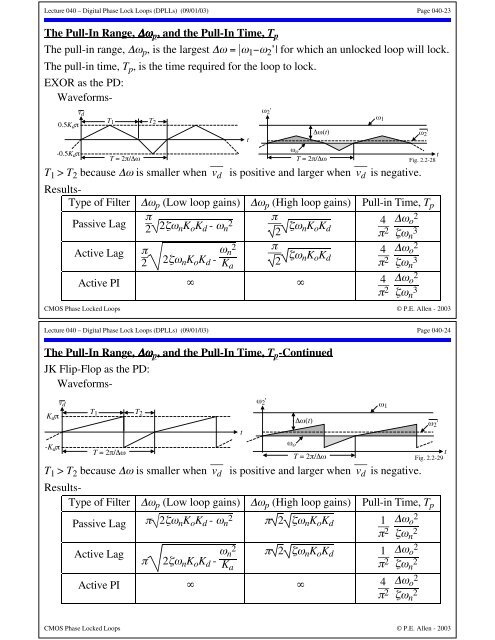

Lecture <strong>040</strong> – Digital Phase Lock Loops (<strong>DPLLs</strong>) (09/01/03) Page <strong>040</strong>-23The Pull-In Range, ∆ω p , and the Pull-In Time, T pThe pull-in range, ∆ω p , is the largest ∆ω = |ω 1 −ω 2 ’| for which an unlocked loop will lock.The pull-in time, T p , is the time required for the loop to lock.EXOR as the PD:Waveformsvd0.5K d π-0.5K d πT 1 T 2T = 2π/∆ωttFig. 2.2-28CMOS Phase Locked Loops © P.E. Allen - 2003ω 2 '∆ω(t)ω oT = 2π/∆ωT 1 > T 2 because ∆ω is smaller when v d is positive and larger when v d is negative.Results-Type of Filter ∆ω p (Low loop gains) ∆ω p (High loop gains) Pull-in Time, T pPassive Lagπ2 2ζω πnK o K d - ω 2 n2 ζω nK o K4 o 2dπ 2 ζω 3 nActive Lag π2 2ζω n K o K d - ω n 2 πK a2 ζω nK o K4 o 2dπ 2 ζω 3 nActive PI ∞ ∞ 4 o 2π 2 ζω 3 nω 1ω 2 'Lecture <strong>040</strong> – Digital Phase Lock Loops (<strong>DPLLs</strong>) (09/01/03) Page <strong>040</strong>-24The Pull-In Range, ∆ω p , and the Pull-In Time, T p -ContinuedJK Flip-Flop as the PD:WaveformsvdK d π-K d πT 1 T 2T = 2π/∆ωtω 2 'ω o∆ω(t)T = 2π/∆ωω 1ω 2 'tFig. 2.2-29T 1 > T 2 because ∆ω is smaller when v d is positive and larger when v d is negative.Results-Type of Filter ∆ω p (Low loop gains) ∆ω p (High loop gains) Pull-in Time, T pPassive Lag π 2ζω n K o K d - ω 2 n π 2 ζω n K o K d 1 o 2π 2 ζω 2 nActive Lagπ 2ζω n K o K d - ω n 2 π 2 ζω n K o K d 1 ∆ω o 2K a π 2 ζω 2 nActive PI ∞ ∞ 4 ∆ω o 2π 2 ζω 2 nCMOS Phase Locked Loops © P.E. Allen - 2003