LECTURE 040 –DIGITAL PHASE LOCK LOOPS (DPLLs)

LECTURE 040 –DIGITAL PHASE LOCK LOOPS (DPLLs)

LECTURE 040 –DIGITAL PHASE LOCK LOOPS (DPLLs)

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

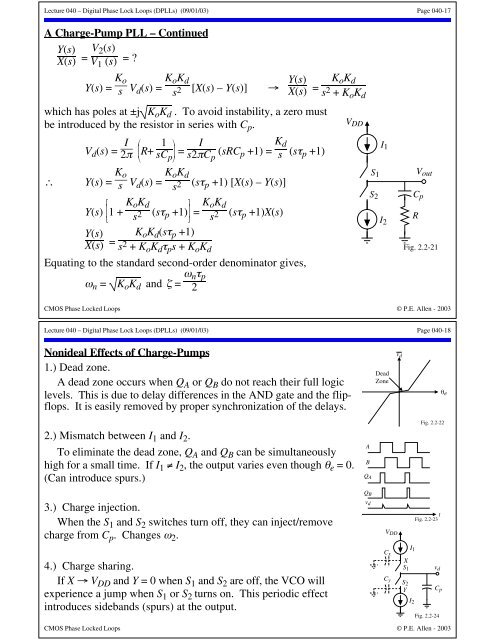

Lecture <strong>040</strong> – Digital Phase Lock Loops (<strong>DPLLs</strong>) (09/01/03) Page <strong>040</strong>-17A Charge-Pump PLL – ContinuedY(s)X(s) = V 2(s)V 1 (s) = ?Y(s) = K os V d(s) = K oK ds 2 [X(s) – Y(s)] → Y(s)X(s) =K o K ds 2 + K o K dwhich has poles at ±j K o K d . To avoid instability, a zero mustbe introduced by the resistor in series with C p .∴V d (s) = I2π⎝ ⎜ ⎜ ⎛R+ 1 IsC = p s2πC (sRC p p +1) = K ds (sτ p +1)⎠ ⎟ ⎟ ⎞Y(s) = K os V d (s) = K oK ds 2 (sτ p +1) [X(s) – Y(s)]⎡⎢Y(s) ⎢ ⎣1 + K oK d⎥s 2 (sτ p +1) = K oK d⎦ s 2 (sτ p +1)X(s)Y(s)X(s) = K o K d (sτ p +1)s 2 + K o K d τ p s + K o K dEquating to the standard second-order denominator gives,ω n = K o K d and ζ = ω nτ p⎤⎥2V DDC pCMOS Phase Locked Loops © P.E. Allen - 2003I 1S1I 2V outS 2RFig. 2.2-21Lecture <strong>040</strong> – Digital Phase Lock Loops (<strong>DPLLs</strong>) (09/01/03) Page <strong>040</strong>-18Nonideal Effects of Charge-Pumps1.) Dead zone.A dead zone occurs when Q A or Q B do not reach their full logiclevels. This is due to delay differences in the AND gate and the flipflops.It is easily removed by proper synchronization of the delays.DeadZonev dθe2.) Mismatch between I 1 and I 2 .To eliminate the dead zone, Q A and Q B can be simultaneouslyhigh for a small time. If I 1 ≠ I 2 , the output varies even though θ e = 0.(Can introduce spurs.)3.) Charge injection.When the S 1 and S 2 switches turn off, they can inject/removecharge from C p . Changes ω 2 .4.) Charge sharing.If X → V DD and Y = 0 when S 1 and S 2 are off, the VCO willexperience a jump when S 1 or S 2 turns on. This periodic effectintroduces sidebands (spurs) at the output.ABQ AQ Bv dV DDFig. 2.2-22tFig. 2.2-23IC 1 xXS 1 v dC y S 2Y C pI 2Fig. 2.2-24CMOS Phase Locked Loops © P.E. Allen - 2003