LECTURE 040 –DIGITAL PHASE LOCK LOOPS (DPLLs)

LECTURE 040 –DIGITAL PHASE LOCK LOOPS (DPLLs)

LECTURE 040 –DIGITAL PHASE LOCK LOOPS (DPLLs)

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

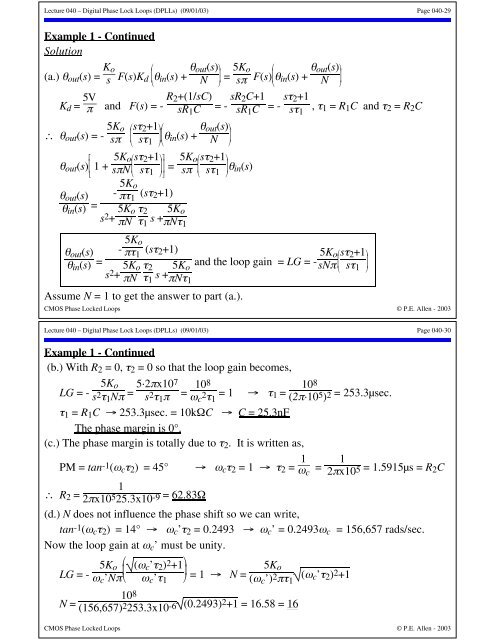

Lecture <strong>040</strong> – Digital Phase Lock Loops (<strong>DPLLs</strong>) (09/01/03) Page <strong>040</strong>-29Example 1 - ContinuedSolution(a.) θ out (s) = K o⎛⎜⎟s F(s)K d ⎜⎟⎝θ in (s) + θ out(s)⎞N = 5K osπ F(s) ⎜ ⎜ ⎛θ⎝ in (s) + θ out(s)N⎠K d = 5V π and F(s) = - R 2+(1/sC)sR 1 C = - sR 2C+1sR 1 C = - sτ 2+1sτ 1, τ 1 = R 1 C and τ 2 = R 2 C∴ θ out (s) = - 5K osπ ⎜ ⎜ ⎛ sτ 2 +1⎝ ⎠ ⎟ ⎟ ⎞ ⎛⎜⎟sτ⎜ 1θ ⎟⎝ in (s) + θ out(s) ⎞N ⎠⎡⎢θ out (s) ⎢ 1 + 5K o⎛sτ ⎜ 2 +1⎞⎣sπN ⎜ ⎝sτ 1= 5K o⎛sτ ⎜ 2 +1⎞⎟sπ ⎜ ⎟ ⎝sτ 1θ in (s)θ out (s)θ in (s) =θ out (s)θ in (s) =⎤⎟⎥⎟⎥⎠⎦- 5K oπτ 1(sτ 2 +1)s 2 + 5K oπN τ 2τ 1s + 5K oπNτ 1- 5K oπτ 1(sτ 2 +1)s2+ 5K o τ 2πN τ 1s + 5K and the loop gain = LG = - 5K o⎜osNπ ⎜ ⎝πNτ 1Assume N = 1 to get the answer to part (a.).⎠CMOS Phase Locked Loops © P.E. Allen - 2003⎛⎠ ⎟ ⎟ ⎞sτ 2 +1⎞sτ 1⎟⎟⎠Lecture <strong>040</strong> – Digital Phase Lock Loops (<strong>DPLLs</strong>) (09/01/03) Page <strong>040</strong>-30Example 1 - Continued(b.) With R 2 = 0, τ 2 = 0 so that the loop gain becomes,5K oLG = - s 2 τ 1 Nπ = 5·2πx107s 2 τ 1 π = 10 8108ω c2τ = 1 → τ 1 1 = (2π·10 5 ) 2 = 253.3µsec.τ 1 = R 1 C → 253.3µsec. = 10kΩC → C = 25.3nFThe phase margin is 0°.(c.) The phase margin is totally due to τ 2 . It is written as,PM = tan -1 (ω c τ 2 ) = 45° → ω c τ 2 = 1 → τ 2 = 1 1ω c= 2πx10 5 = 1.5915µs = R 2 C1∴ R 2 = 2πx10525.3x10-9 = 62.83Ω(d.) N does not influence the phase shift so we can write,tan -1 (ω c τ 2 ) = 14° → ω c ’τ 2 = 0.2493 → ω c ’ = 0.2493ω c = 156,657 rads/sec.Now the loop gain at ω c ’ must be unity.LG = -N =5K oω c ’Nπ⎝ ⎜⎛(ω c ’τ 2 ) 2 +1ω ⎠ ⎟⎞5K oc ’τ 1= 1 → N = (ω c ’)2πτ 1(ω c ’τ 2 ) 2 +110 8(156,657) 2 253.3x10 -6 (0.2493) 2 +1 = 16.58 = 16CMOS Phase Locked Loops © P.E. Allen - 2003