iAPX 286 Operating System Writers Guide 1983

iAPX 286 Operating System Writers Guide 1983

iAPX 286 Operating System Writers Guide 1983

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

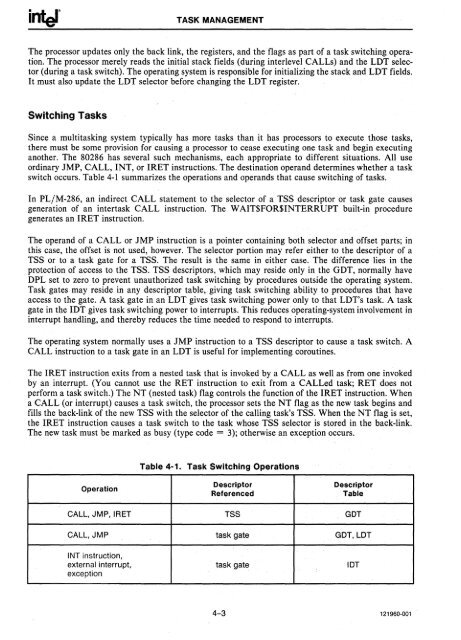

TASK MANAGEMENTThe processor updates only the back link, the registers, and the flags as part of a task switching operation.The processor merely reads the initial stack fields (during interlevel CALLs) and the LDT selector(during a task switch). The operating system is responsible for initializing the stack and LDT fields.It must also update the LDT selector before changing the LDT register.Switching TasksSince a multitasking system typically has more tasks than it has processors to execute those tasks,there must be some provision for causing a processor to cease executing one task and begin executinganother. The 80<strong>286</strong> has several such mechanisms, each appropriate to different situations. All useordinary JMP, CALL, INT, or IRET instructions. The destination operand determines whether a taskswitch occurs. Table 4-1 summarizes the operations and operands that cause switching of tasks.In PL/M-<strong>286</strong>, an indirect CALL statement to the selector of a TSS descriptor or task gate causesgeneration of an intertask CALL instruction. The W AIT$FOR$INTERRUPT built-in proceduregenerates an IRET instruction.The operand of a CALL or JMP instruction is a pointer containing both selector and offset parts; inthis case, the offset is not used, however. The selector portion may refer either to the descriptor of aTSS or to a task gate for a TSS. The result is the same in either case. The difference lies in theprotection of access to the TSS. TSS descriptors, which may reside only in the GDT, normally haveDPL set to zero to prevent unauthorized task switching by procedures outside the operating system.Task gates may reside in any descriptor table, giving task switching ability to procedures that haveaccess to the gate. A task gate in an LDT gives task switching power only to that LDT's task. A taskgate in the IDT gives task switching power to interrupts. This reduces operating-system involvement ininterrupt handling, and thereby reduces the time needed to respond to interrupts.The operating system normally uses a JMP instruction to a TSS descriptor to cause a task switch. ACALL instruction to a task gate in an LDT is useful for implementing coroutines.The IRET instruction exits from a nested task that is invoked by a CALL as well as from one invokedby an interrupt. (You cannot use the RET instruction to exit from a CALLed task; RET does notperform a task switch.) The NT (nested task) flag controls the function of the IRET instruction. Whena CALL (or interrupt) causes a task switch, the processor sets the NT flag as the new task begins andfills the back-link of the new TSS with the selector of the calling task's TSS. When the NT flag is set,the IRET instruction causes a task switch to the task whose TSS selector is stored in the back-link.The new task must be marked as busy (type code = 3); otherwise an exception occurs.Table 4-1. Task Switching OperationsOperationDescriptorReferencedDescriptorTableCALL, JMP, IRET TSS GOTCALL, JMP task gate GOT, LOTINT instruction,external interrupt, task gate lOTexception4-3 121960·001