Xilinx 4000-series FPGAs

Xilinx 4000-series FPGAs

Xilinx 4000-series FPGAs

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

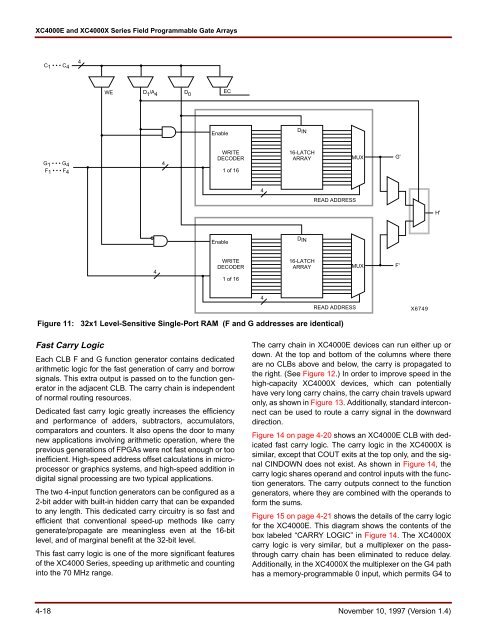

XC<strong>4000</strong>E and XC<strong>4000</strong>X Series Field Programmable Gate ArraysC 1 • • • C 44WE D 1 /A 4 D 0ECEnableDING 1 • • • G 4F 1 • • • F 44WRITEDECODER1 of 1616-LATCHARRAYMUXG'4READ ADDRESSH'EnableDIN4WRITEDECODER1 of 1616-LATCHARRAYMUXF'4READ ADDRESSX6749Figure 11: 32x1 Level-Sensitive Single-Port RAM (F and G addresses are identical)Fast Carry LogicEach CLB F and G function generator contains dedicatedarithmetic logic for the fast generation of carry and borrowsignals. This extra output is passed on to the function generatorin the adjacent CLB. The carry chain is independentof normal routing resources.Dedicated fast carry logic greatly increases the efficiencyand performance of adders, subtractors, accumulators,comparators and counters. It also opens the door to manynew applications involving arithmetic operation, where theprevious generations of <strong>FPGAs</strong> were not fast enough or tooinefficient. High-speed address offset calculations in microprocessoror graphics systems, and high-speed addition indigital signal processing are two typical applications.The two 4-input function generators can be configured as a2-bit adder with built-in hidden carry that can be expandedto any length. This dedicated carry circuitry is so fast andefficient that conventional speed-up methods like carrygenerate/propagate are meaningless even at the 16-bitlevel, and of marginal benefit at the 32-bit level.This fast carry logic is one of the more significant featuresof the XC<strong>4000</strong> Series, speeding up arithmetic and countinginto the 70 MHz range.The carry chain in XC<strong>4000</strong>E devices can run either up ordown. At the top and bottom of the columns where thereare no CLBs above and below, the carry is propagated tothe right. (See Figure 12.) In order to improve speed in thehigh-capacity XC<strong>4000</strong>X devices, which can potentiallyhave very long carry chains, the carry chain travels upwardonly, as shown in Figure 13. Additionally, standard interconnectcan be used to route a carry signal in the downwarddirection.Figure 14 on page 4-20 shows an XC<strong>4000</strong>E CLB with dedicatedfast carry logic. The carry logic in the XC<strong>4000</strong>X issimilar, except that COUT exits at the top only, and the signalCINDOWN does not exist. As shown in Figure 14, thecarry logic shares operand and control inputs with the functiongenerators. The carry outputs connect to the functiongenerators, where they are combined with the operands toform the sums.Figure 15 on page 4-21 shows the details of the carry logicfor the XC<strong>4000</strong>E. This diagram shows the contents of thebox labeled “CARRY LOGIC” in Figure 14. The XC<strong>4000</strong>Xcarry logic is very similar, but a multiplexer on the passthroughcarry chain has been eliminated to reduce delay.Additionally, in the XC<strong>4000</strong>X the multiplexer on the G4 pathhas a memory-programmable 0 input, which permits G4 to4-18 November 10, 1997 (Version 1.4)