Xilinx 4000-series FPGAs

Xilinx 4000-series FPGAs

Xilinx 4000-series FPGAs

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

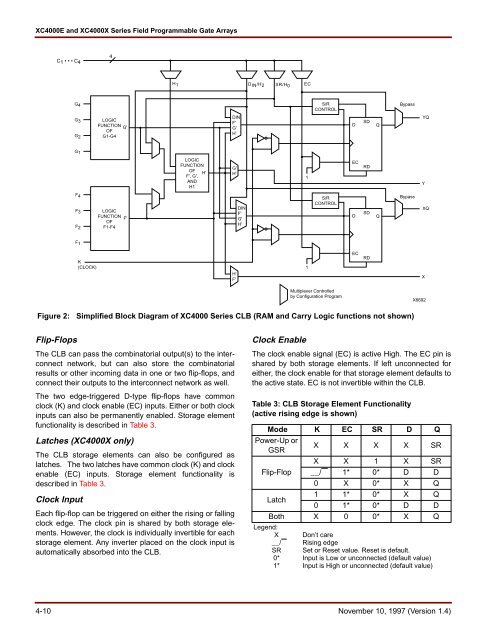

XC<strong>4000</strong>E and XC<strong>4000</strong>X Series Field Programmable Gate ArraysC 1 • • • C 44H 1 D IN /H 2 SR/H0 ECG 4G 3G 2LOGICFUNCTIONG'OFG1-G4DINF'G'H'S/RCONTROLDSDQBypassYQG 1LOGICFUNCTIONOFH'F', G',ANDH1G'H'1YECRDBypassF 4F 3F 2LOGICFUNCTIONOFF1-F4F'DINF'G'H'S/RCONTROLDSDQXQF 1K(CLOCK)H'F'1ECRDXMultiplexer Controlledby Configuration ProgramX6692Figure 2: Simplified Block Diagram of XC<strong>4000</strong> Series CLB (RAM and Carry Logic functions not shown)Flip-FlopsThe CLB can pass the combinatorial output(s) to the interconnectnetwork, but can also store the combinatorialresults or other incoming data in one or two flip-flops, andconnect their outputs to the interconnect network as well.The two edge-triggered D-type flip-flops have commonclock (K) and clock enable (EC) inputs. Either or both clockinputs can also be permanently enabled. Storage elementfunctionality is described in Table 3.Latches (XC<strong>4000</strong>X only)The CLB storage elements can also be configured aslatches. The two latches have common clock (K) and clockenable (EC) inputs. Storage element functionality isdescribed in Table 3.Clock InputEach flip-flop can be triggered on either the rising or fallingclock edge. The clock pin is shared by both storage elements.However, the clock is individually invertible for eachstorage element. Any inverter placed on the clock input isautomatically absorbed into the CLB.Clock EnableThe clock enable signal (EC) is active High. The EC pin isshared by both storage elements. If left unconnected foreither, the clock enable for that storage element defaults tothe active state. EC is not invertible within the CLB.Table 3: CLB Storage Element Functionality(active rising edge is shown)Mode K EC SR D QPower-Up orGSRX X X X SRX X 1 X SRFlip-Flop __/ 1* 0* D D0 X 0* X QLatch1 1* 0* X Q0 1* 0* D DBoth X 0 0* X QLegend:X__/SR0*1*Don’t careRising edgeSet or Reset value. Reset is default.Input is Low or unconnected (default value)Input is High or unconnected (default value)4-10 November 10, 1997 (Version 1.4)