Xilinx 4000-series FPGAs

Xilinx 4000-series FPGAs

Xilinx 4000-series FPGAs

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

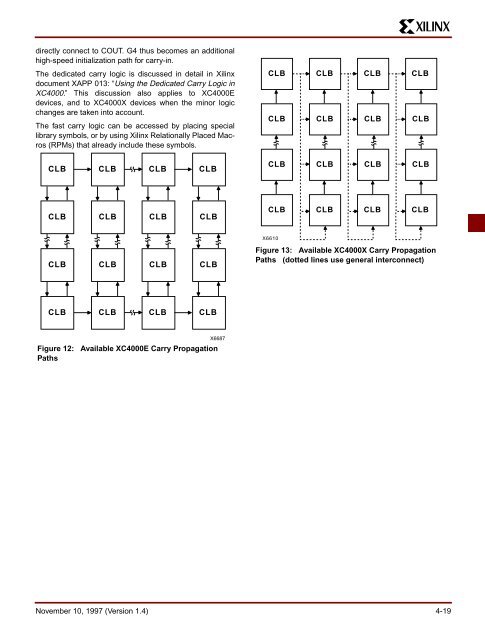

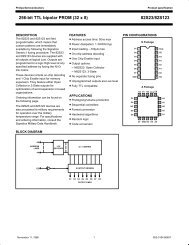

directly connect to COUT. G4 thus becomes an additionalhigh-speed initialization path for carry-in.The dedicated carry logic is discussed in detail in <strong>Xilinx</strong>document XAPP 013: “Using the Dedicated Carry Logic inXC<strong>4000</strong>.” This discussion also applies to XC<strong>4000</strong>Edevices, and to XC<strong>4000</strong>X devices when the minor logicchanges are taken into account.The fast carry logic can be accessed by placing speciallibrary symbols, or by using <strong>Xilinx</strong> Relationally Placed Macros(RPMs) that already include these symbols.CLB CLB CLB CLBCLB CLB CLB CLBCLB CLB CLB CLBCLBCLBCLBCLBCLBCLBCLBCLBCLB CLB CLB CLBX6610CLBCLBCLBCLBFigure 13: Available XC<strong>4000</strong>X Carry PropagationPaths (dotted lines use general interconnect)CLB CLB CLB CLBFigure 12: Available XC<strong>4000</strong>E Carry PropagationPathsX6687November 10, 1997 (Version 1.4) 4-19