PHYSIOLOGICAL-READOUT

ISSCC2017AdvanceProgram

ISSCC2017AdvanceProgram

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

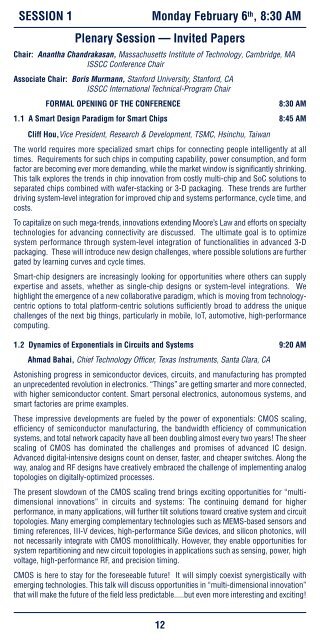

SESSION 1<br />

Monday February 6 th , 8:30 AM<br />

Plenary Session — Invited Papers<br />

Chair: Anantha Chandrakasan, Massachusetts Institute of Technology, Cambridge, MA<br />

ISSCC Conference Chair<br />

Associate Chair: Boris Murmann, Stanford University, Stanford, CA<br />

ISSCC International Technical-Program Chair<br />

FORMAL OPENING OF THE CONFERENCE<br />

8:30 AM<br />

1.1 A Smart Design Paradigm for Smart Chips 8:45 AM<br />

Cliff Hou,Vice President, Research & Development, TSMC, Hsinchu, Taiwan<br />

The world requires more specialized smart chips for connecting people intelligently at all<br />

times. Requirements for such chips in computing capability, power consumption, and form<br />

factor are becoming ever more demanding, while the market window is significantly shrinking.<br />

This talk explores the trends in chip innovation from costly multi-chip and SoC solutions to<br />

separated chips combined with wafer-stacking or 3-D packaging. These trends are further<br />

driving system-level integration for improved chip and systems performance, cycle time, and<br />

costs.<br />

To capitalize on such mega-trends, innovations extending Moore’s Law and efforts on specialty<br />

technologies for advancing connectivity are discussed. The ultimate goal is to optimize<br />

system performance through system-level integration of functionalities in advanced 3-D<br />

packaging. These will introduce new design challenges, where possible solutions are further<br />

gated by learning curves and cycle times.<br />

Smart-chip designers are increasingly looking for opportunities where others can supply<br />

expertise and assets, whether as single-chip designs or system-level integrations. We<br />

highlight the emergence of a new collaborative paradigm, which is moving from technologycentric<br />

options to total platform-centric solutions sufficiently broad to address the unique<br />

challenges of the next big things, particularly in mobile, IoT, automotive, high-performance<br />

computing.<br />

1.2 Dynamics of Exponentials in Circuits and Systems 9:20 AM<br />

Ahmad Bahai, Chief Technology Officer, Texas Instruments, Santa Clara, CA<br />

Astonishing progress in semiconductor devices, circuits, and manufacturing has prompted<br />

an unprecedented revolution in electronics. “Things” are getting smarter and more connected,<br />

with higher semiconductor content. Smart personal electronics, autonomous systems, and<br />

smart factories are prime examples.<br />

These impressive developments are fueled by the power of exponentials: CMOS scaling,<br />

efficiency of semiconductor manufacturing, the bandwidth efficiency of communication<br />

systems, and total network capacity have all been doubling almost every two years! The sheer<br />

scaling of CMOS has dominated the challenges and promises of advanced IC design.<br />

Advanced digital-intensive designs count on denser, faster, and cheaper switches. Along the<br />

way, analog and RF designs have creatively embraced the challenge of implementing analog<br />

topologies on digitally-optimized processes.<br />

The present slowdown of the CMOS scaling trend brings exciting opportunities for “multidimensional<br />

innovations” in circuits and systems: The continuing demand for higher<br />

performance, in many applications, will further tilt solutions toward creative system and circuit<br />

topologies. Many emerging complementary technologies such as MEMS-based sensors and<br />

timing references, III-V devices, high-performance SiGe devices, and silicon photonics, will<br />

not necessarily integrate with CMOS monolithically. However, they enable opportunities for<br />

system repartitioning and new circuit topologies in applications such as sensing, power, high<br />

voltage, high-performance RF, and precision timing.<br />

CMOS is here to stay for the foreseeable future! It will simply coexist synergistically with<br />

emerging technologies. This talk will discuss opportunities in “multi-dimensional innovation”<br />

that will make the future of the field less predictable.....but even more interesting and exciting!<br />

12