PHYSIOLOGICAL-READOUT

ISSCC2017AdvanceProgram

ISSCC2017AdvanceProgram

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

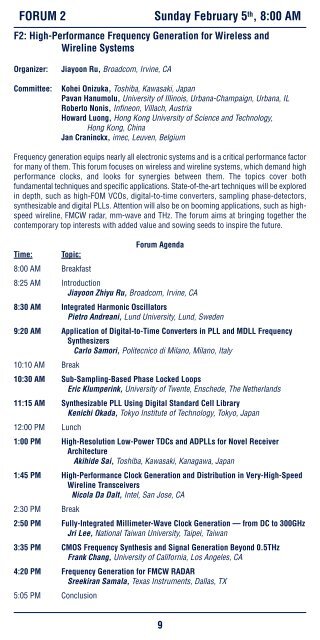

FORUM 2<br />

Sunday February 5 th , 8:00 AM<br />

F2: High-Performance Frequency Generation for Wireless and<br />

Wireline Systems<br />

Organizer:<br />

Committee:<br />

Jiayoon Ru, Broadcom, Irvine, CA<br />

Kohei Onizuka, Toshiba, Kawasaki, Japan<br />

Pavan Hanumolu, University of Illinois, Urbana-Champaign, Urbana, IL<br />

Roberto Nonis, Infineon, Villach, Austria<br />

Howard Luong, Hong Kong University of Science and Technology,<br />

Hong Kong, China<br />

Jan Craninckx, imec, Leuven, Belgium<br />

Frequency generation equips nearly all electronic systems and is a critical performance factor<br />

for many of them. This forum focuses on wireless and wireline systems, which demand high<br />

performance clocks, and looks for synergies between them. The topics cover both<br />

fundamental techniques and specific applications. State-of-the-art techniques will be explored<br />

in depth, such as high-FOM VCOs, digital-to-time converters, sampling phase-detectors,<br />

synthesizable and digital PLLs. Attention will also be on booming applications, such as highspeed<br />

wireline, FMCW radar, mm-wave and THz. The forum aims at bringing together the<br />

contemporary top interests with added value and sowing seeds to inspire the future.<br />

Forum Agenda<br />

Time: Topic:<br />

8:00 AM Breakfast<br />

8:25 AM Introduction<br />

Jiayoon Zhiyu Ru, Broadcom, Irvine, CA<br />

8:30 AM Integrated Harmonic Oscillators<br />

Pietro Andreani, Lund University, Lund, Sweden<br />

9:20 AM Application of Digital-to-Time Converters in PLL and MDLL Frequency<br />

Synthesizers<br />

Carlo Samori, Politecnico di Milano, Milano, Italy<br />

10:10 AM Break<br />

10:30 AM Sub-Sampling-Based Phase Locked Loops<br />

Eric Klumperink, University of Twente, Enschede, The Netherlands<br />

11:15 AM Synthesizable PLL Using Digital Standard Cell Library<br />

Kenichi Okada, Tokyo Institute of Technology, Tokyo, Japan<br />

12:00 PM Lunch<br />

1:00 PM High-Resolution Low-Power TDCs and ADPLLs for Novel Receiver<br />

Architecture<br />

Akihide Sai, Toshiba, Kawasaki, Kanagawa, Japan<br />

1:45 PM High-Performance Clock Generation and Distribution in Very-High-Speed<br />

Wireline Transceivers<br />

Nicola Da Dalt, Intel, San Jose, CA<br />

2:30 PM Break<br />

2:50 PM Fully-Integrated Millimeter-Wave Clock Generation — from DC to 300GHz<br />

Jri Lee, National Taiwan University, Taipei, Taiwan<br />

3:35 PM CMOS Frequency Synthesis and Signal Generation Beyond 0.5THz<br />

Frank Chang, University of California, Los Angeles, CA<br />

4:20 PM Frequency Generation for FMCW RADAR<br />

Sreekiran Samala, Texas Instruments, Dallas, TX<br />

5:05 PM Conclusion<br />

9