PHYSIOLOGICAL-READOUT

ISSCC2017AdvanceProgram

ISSCC2017AdvanceProgram

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

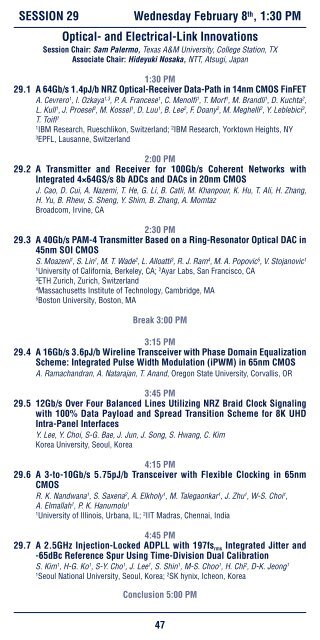

SESSION 29<br />

Wednesday February 8 th , 1:30 PM<br />

Optical- and Electrical-Link Innovations<br />

Session Chair: Sam Palermo, Texas A&M University, College Station, TX<br />

Associate Chair: Hideyuki Nosaka, NTT, Atsugi, Japan<br />

1:30 PM<br />

29.1 A 64Gb/s 1.4pJ/b NRZ Optical-Receiver Data-Path in 14nm CMOS FinFET<br />

A. Cevrero 1 , I. Ozkaya 1,3 , P. A. Francese 1 , C. Menolfi 1 , T. Morf 1 , M. Brandli 1 , D. Kuchta 2 ,<br />

L. Kull 1 , J. Proesel 2 , M. Kossel 1 , D. Luu 1 , B. Lee 2 , F. Doany 2 , M. Meghelli 2 , Y. Leblebici 3 ,<br />

T. Toifl 1<br />

1<br />

IBM Research, Rueschlikon, Switzerland; 2 IBM Research, Yorktown Heights, NY<br />

3<br />

EPFL, Lausanne, Switzerland<br />

2:00 PM<br />

29.2 A Transmitter and Receiver for 100Gb/s Coherent Networks with<br />

Integrated 4×64GS/s 8b ADCs and DACs in 20nm CMOS<br />

J. Cao, D. Cui, A. Nazemi, T. He, G. Li, B. Catli, M. Khanpour, K. Hu, T. Ali, H. Zhang,<br />

H. Yu, B. Rhew, S. Sheng, Y. Shim, B. Zhang, A. Momtaz<br />

Broadcom, Irvine, CA<br />

2:30 PM<br />

29.3 A 40Gb/s PAM-4 Transmitter Based on a Ring-Resonator Optical DAC in<br />

45nm SOI CMOS<br />

S. Moazeni 1 , S. Lin 1 , M. T. Wade 2 , L. Alloatti 3 , R. J. Ram 4 , M. A. Popovic 5 , V. Stojanovic 1<br />

1<br />

University of California, Berkeley, CA; 2 Ayar Labs, San Francisco, CA<br />

3<br />

ETH Zurich, Zurich, Switzerland<br />

4<br />

Massachusetts Institute of Technology, Cambridge, MA<br />

5<br />

Boston University, Boston, MA<br />

Break 3:00 PM<br />

3:15 PM<br />

29.4 A 16Gb/s 3.6pJ/b Wireline Transceiver with Phase Domain Equalization<br />

Scheme: Integrated Pulse Width Modulation (iPWM) in 65nm CMOS<br />

A. Ramachandran, A. Natarajan, T. Anand, Oregon State University, Corvallis, OR<br />

3:45 PM<br />

29.5 12Gb/s Over Four Balanced Lines Utilizing NRZ Braid Clock Signaling<br />

with 100% Data Payload and Spread Transition Scheme for 8K UHD<br />

Intra-Panel Interfaces<br />

Y. Lee, Y. Choi, S-G. Bae, J. Jun, J. Song, S. Hwang, C. Kim<br />

Korea University, Seoul, Korea<br />

4:15 PM<br />

29.6 A 3-to-10Gb/s 5.75pJ/b Transceiver with Flexible Clocking in 65nm<br />

CMOS<br />

R. K. Nandwana 1 , S. Saxena 2 , A. Elkholy 1 , M. Talegaonkar 1 , J. Zhu 1 , W-S. Choi 1 ,<br />

A. Elmallah 1 , P. K. Hanumolu 1<br />

1<br />

University of Illinois, Urbana, IL; 2 IIT Madras, Chennai, India<br />

4:45 PM<br />

29.7 A 2.5GHz Injection-Locked ADPLL with 197fs rms Integrated Jitter and<br />

-65dBc Reference Spur Using Time-Division Dual Calibration<br />

S. Kim 1 , H-G. Ko 1 , S-Y. Cho 1 , J. Lee 1 , S. Shin 1 , M-S. Choo 1 , H. Chi 2 , D-K. Jeong 1<br />

1<br />

Seoul National University, Seoul, Korea; 2 SK hynix, Icheon, Korea<br />

Conclusion 5:00 PM<br />

47