PHYSIOLOGICAL-READOUT

ISSCC2017AdvanceProgram

ISSCC2017AdvanceProgram

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

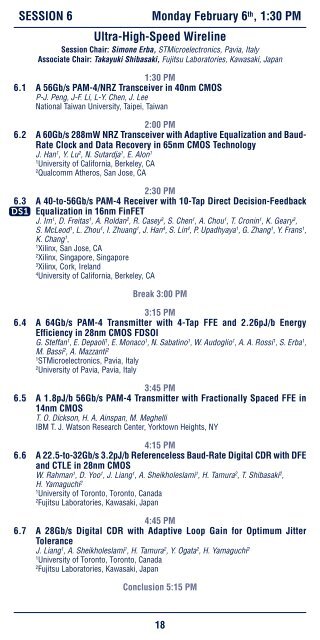

SESSION 6<br />

Ultra-High-Speed Wireline<br />

Session Chair: Simone Erba, STMicroelectronics, Pavia, Italy<br />

Associate Chair: Takayuki Shibasaki, Fujitsu Laboratories, Kawasaki, Japan<br />

1:30 PM<br />

6.1 A 56Gb/s PAM-4/NRZ Transceiver in 40nm CMOS<br />

P-J. Peng, J-F. Li, L-Y. Chen, J. Lee<br />

National Taiwan University, Taipei, Taiwan<br />

Monday February 6 th , 1:30 PM<br />

2:00 PM<br />

6.2 A 60Gb/s 288mW NRZ Transceiver with Adaptive Equalization and Baud-<br />

Rate Clock and Data Recovery in 65nm CMOS Technology<br />

J. Han 1 , Y. Lu 2 , N. Sutardja 1 , E. Alon 1<br />

1<br />

University of California, Berkeley, CA<br />

2<br />

Qualcomm Atheros, San Jose, CA<br />

2:30 PM<br />

6.3 A 40-to-56Gb/s PAM-4 Receiver with 10-Tap Direct Decision-Feedback<br />

DS1 Equalization in 16nm FinFET<br />

J. Im 1 , D. Freitas 1 , A. Roldan 2 , R. Casey 3 , S. Chen 1 , A. Chou 1 , T. Cronin 1 , K. Geary 3 ,<br />

S. McLeod 1 , L. Zhou 1 , I. Zhuang 1 , J. Han 4 , S. Lin 4 , P. Upadhyaya 1 , G. Zhang 1 , Y. Frans 1 ,<br />

K. Chang 1 ,<br />

1<br />

Xilinx, San Jose, CA<br />

2<br />

Xilinx, Singapore, Singapore<br />

3<br />

Xilinx, Cork, Ireland<br />

4<br />

University of California, Berkeley, CA<br />

Break 3:00 PM<br />

3:15 PM<br />

6.4 A 64Gb/s PAM-4 Transmitter with 4-Tap FFE and 2.26pJ/b Energy<br />

Efficiency in 28nm CMOS FDSOI<br />

G. Steffan 1 , E. Depaoli 1 , E. Monaco 1 , N. Sabatino 1 , W. Audoglio 1 , A. A. Rossi 1 , S. Erba 1 ,<br />

M. Bassi 2 , A. Mazzanti 2<br />

1<br />

STMicroelectronics, Pavia, Italy<br />

2<br />

University of Pavia, Pavia, Italy<br />

3:45 PM<br />

6.5 A 1.8pJ/b 56Gb/s PAM-4 Transmitter with Fractionally Spaced FFE in<br />

14nm CMOS<br />

T. O. Dickson, H. A. Ainspan, M. Meghelli<br />

IBM T. J. Watson Research Center, Yorktown Heights, NY<br />

4:15 PM<br />

6.6 A 22.5-to-32Gb/s 3.2pJ/b Referenceless Baud-Rate Digital CDR with DFE<br />

and CTLE in 28nm CMOS<br />

W. Rahman 1 , D. Yoo 1 , J. Liang 1 , A. Sheikholeslami 1 , H. Tamura 2 , T. Shibasaki 2 ,<br />

H. Yamaguchi 2<br />

1<br />

University of Toronto, Toronto, Canada<br />

2<br />

Fujitsu Laboratories, Kawasaki, Japan<br />

4:45 PM<br />

6.7 A 28Gb/s Digital CDR with Adaptive Loop Gain for Optimum Jitter<br />

Tolerance<br />

J. Liang 1 , A. Sheikholeslami 1 , H. Tamura 2 , Y. Ogata 2 , H. Yamaguchi 2<br />

1<br />

University of Toronto, Toronto, Canada<br />

2<br />

Fujitsu Laboratories, Kawasaki, Japan<br />

Conclusion 5:15 PM<br />

18