PHYSIOLOGICAL-READOUT

ISSCC2017AdvanceProgram

ISSCC2017AdvanceProgram

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

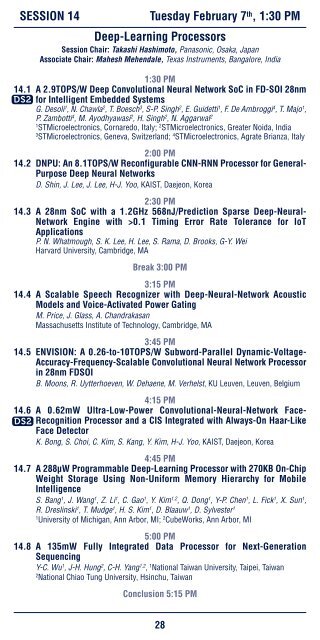

SESSION 14<br />

Tuesday February 7 th , 1:30 PM<br />

Deep-Learning Processors<br />

Session Chair: Takashi Hashimoto, Panasonic, Osaka, Japan<br />

Associate Chair: Mahesh Mehendale, Texas Instruments, Bangalore, India<br />

1:30 PM<br />

14.1 A 2.9TOPS/W Deep Convolutional Neural Network SoC in FD-SOI 28nm<br />

DS2 for Intelligent Embedded Systems<br />

G. Desoli 1 , N. Chawla 2 , T. Boesch 3 , S-P. Singh 2 , E. Guidetti 1 , F. De Ambroggi 4 , T. Majo 1 ,<br />

P. Zambotti 4 , M. Ayodhyawasi 2 , H. Singh 2 , N. Aggarwal 2<br />

1<br />

STMicroelectronics, Cornaredo, Italy; 2 STMicroelectronics, Greater Noida, India<br />

3<br />

STMicroelectronics, Geneva, Switzerland; 4 STMicroelectronics, Agrate Brianza, Italy<br />

2:00 PM<br />

14.2 DNPU: An 8.1TOPS/W Reconfigurable CNN-RNN Processor for General-<br />

Purpose Deep Neural Networks<br />

D. Shin, J. Lee, J. Lee, H-J. Yoo, KAIST, Daejeon, Korea<br />

2:30 PM<br />

14.3 A 28nm SoC with a 1.2GHz 568nJ/Prediction Sparse Deep-Neural-<br />

Network Engine with >0.1 Timing Error Rate Tolerance for IoT<br />

Applications<br />

P. N. Whatmough, S. K. Lee, H. Lee, S. Rama, D. Brooks, G-Y. Wei<br />

Harvard University, Cambridge, MA<br />

Break 3:00 PM<br />

3:15 PM<br />

14.4 A Scalable Speech Recognizer with Deep-Neural-Network Acoustic<br />

Models and Voice-Activated Power Gating<br />

M. Price, J. Glass, A. Chandrakasan<br />

Massachusetts Institute of Technology, Cambridge, MA<br />

3:45 PM<br />

14.5 ENVISION: A 0.26-to-10TOPS/W Subword-Parallel Dynamic-Voltage-<br />

Accuracy-Frequency-Scalable Convolutional Neural Network Processor<br />

in 28nm FDSOI<br />

B. Moons, R. Uytterhoeven, W. Dehaene, M. Verhelst, KU Leuven, Leuven, Belgium<br />

4:15 PM<br />

14.6 A 0.62mW Ultra-Low-Power Convolutional-Neural-Network Face-<br />

DS2 Recognition Processor and a CIS Integrated with Always-On Haar-Like<br />

Face Detector<br />

K. Bong, S. Choi, C. Kim, S. Kang, Y. Kim, H-J. Yoo, KAIST, Daejeon, Korea<br />

4:45 PM<br />

14.7 A 288µW Programmable Deep-Learning Processor with 270KB On-Chip<br />

Weight Storage Using Non-Uniform Memory Hierarchy for Mobile<br />

Intelligence<br />

S. Bang 1 , J. Wang 1 , Z. Li 1 , C. Gao 1 , Y. Kim 1,2 , Q. Dong 1 , Y-P. Chen 1 , L. Fick 1 , X. Sun 1 ,<br />

R. Dreslinski 1 , T. Mudge 1 , H. S. Kim 1 , D. Blaauw 1 , D. Sylvester 1<br />

1<br />

University of Michigan, Ann Arbor, MI; 2 CubeWorks, Ann Arbor, MI<br />

5:00 PM<br />

14.8 A 135mW Fully Integrated Data Processor for Next-Generation<br />

Sequencing<br />

Y-C. Wu 1 , J-H. Hung 2 , C-H. Yang 1,2 , 1 National Taiwan University, Taipei, Taiwan<br />

2<br />

National Chiao Tung University, Hsinchu, Taiwan<br />

Conclusion 5:15 PM<br />

28